MIL1553B IP Core

MIL-STD-1553B is a military specification for a Digital Time Division Command/Response Data Bus, featuring half-duplex, Mancheste…

Overview

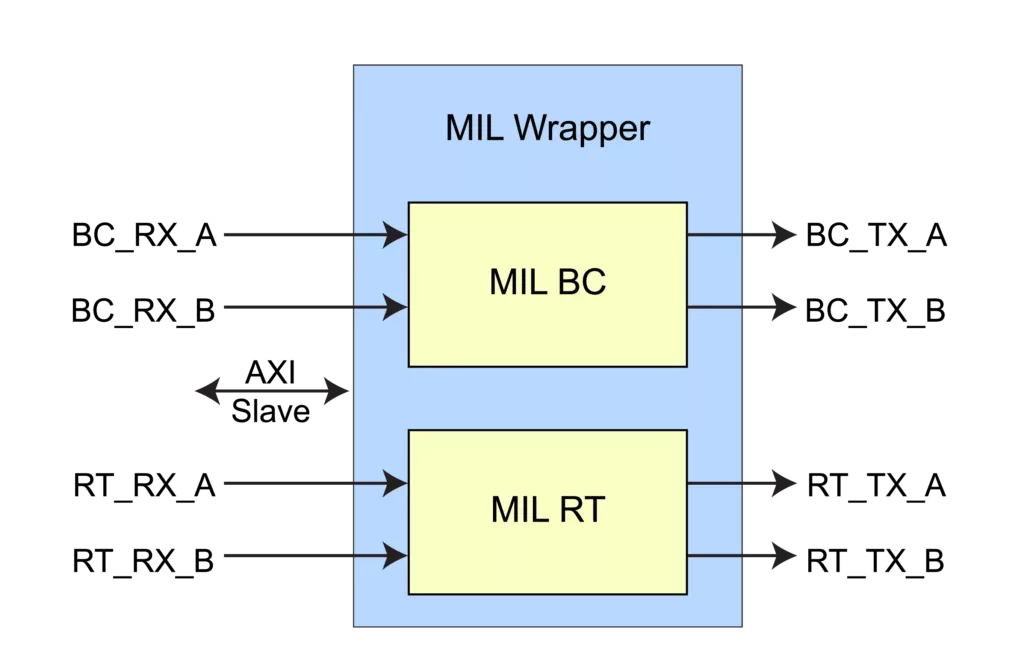

MIL-STD-1553B is a military specification for a Digital Time Division Command/Response Data Bus, featuring half-duplex, Manchester II encoding. A main bus controller (BC) manages communication, while remote terminals (RTs) respond. It defines terminal operations, word structure, messaging protocol, and electrical characteristics.

Key features

- High bit error reliability

- Dual redundancy : Two buses supported

- BC, RT and BM Modes are supported.

- Manchester II encoding

- Parity & Gap generators & checkers for high data integrity

- AXI4 Compatibility for user interface

- IP portable to any available standard FPGA

- 1 Megabit per sec (Mbps) transfer rate

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Mil Std 1553 IP core

Frequently asked questions about MIL-STD-1553 IP cores

What is MIL1553B IP Core?

MIL1553B IP Core is a Mil Std 1553 IP core from Logic Fruit Technologies listed on Semi IP Hub.

How should engineers evaluate this Mil Std 1553?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mil Std 1553 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.