Manchester Encoder / Decoder

The MAN_CODEC IP Core is a versatile encoder and decoder pair that converts a basic NRZ bitstream into a standard Manchester code…

Overview

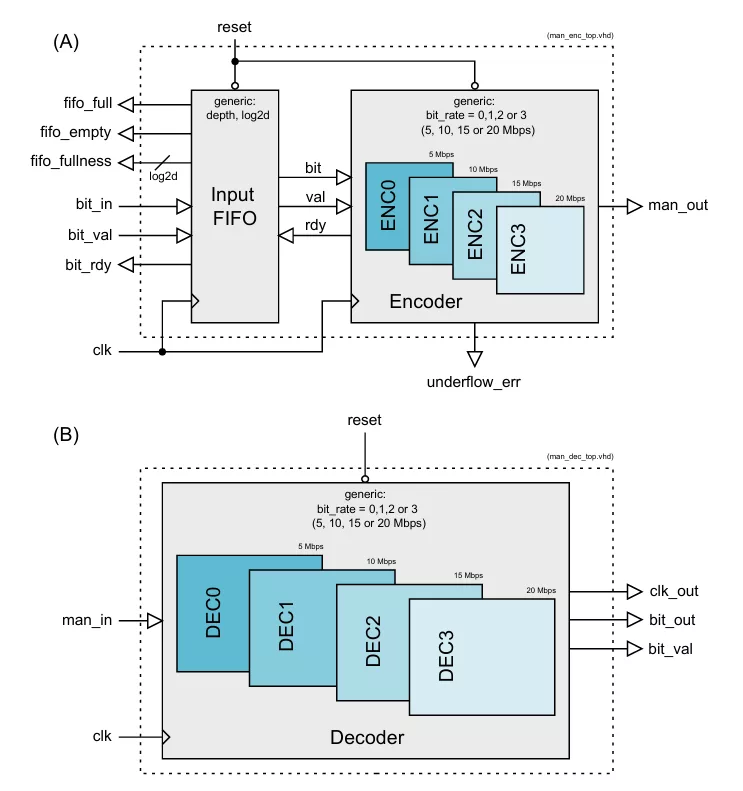

The MAN_CODEC IP Core is a versatile encoder and decoder pair that converts a basic NRZ bitstream into a standard Manchester code and vice-versa. The encoder and decoder are provided as separate IP Cores and, as such, may be used independently or together as a combined codec unit.

Both the encoder and decoder work from a single synchronous clock input (clk) running at a fixed frequency of 240 MHz. In addition there are four different bit rates to choose from. These are: 5, 10, 15 and 20 Mbps. The bit rate setting is fixed at compile time and is controlled by the bit_rate parameter.

Key features

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human readable VHDL (or Verilog) source code

- Encodes a simple NRZ bitstream to the equivalent Manchester code and vice-versa

- Supplied as separate, independent encoder and decoder IP Cores

- DC-balanced encoding suitable for AC-coupling over large distances

- Ideal for serial comms over twisted pair or coaxial

- Encoder features an input FIFO for buffering the incoming bitstream / data packet

- Robust data and clock recovery at the decoder featuring Gaussian pulse-shaping filters for optimum SNR and noise immunity

- No complex PLL setup required. Whole design runs off a single source clock of 240 MHz

- Configurable bit rate setting of 5,10,15 or 20 Mbps on low-cost FPGAs and SoC devices

Block Diagram

Applications

- Applications requiring low-to-medium serial bandwidth

- Industrial / scientific / medical / automotive control systems

- Implementation of robust serial links on low cost devices requiring only a single bit lane

- Galvanically isolated serial links where the DC-component must be zero

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is Manchester Encoder / Decoder?

Manchester Encoder / Decoder is a Channel Coding IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.