Low-power 32-bit RISC-V processor

The icyflex-V 32-bit processor core is based on the RV32IMC open-instruction set architecture (ISA) defined by the RISC-V foundat…

Overview

The icyflex-V 32-bit processor core is based on the RV32IMC open-instruction set architecture (ISA) defined by the RISC-V foundation and, as such, is supported by standard state-of-the-art development tools (both open-source and proprietary). The 4-stage pipeline is optimized for power and area efficiency.

Additional customizations are available on demand (e.g. RV32E area efficient implementation).

The icyflex-V core targets traditional micro-controller applications and is well suited for IoT, wearables and mixed signal applications.

The core IP comes along with various bus interconnect IP’s and standard peripherals. For example, implementations relying on an embedded flash will benefit from an energy oriented cache architecture.

Key features

- RISC-V RV32 instruction set:

- I > full support

- M > partial support: no hardware divider

- C > full support

- Machine mode only

- 32 vectorized interrupts

- Standard debug as defined per RISC-V

- 3.06 CoreMark/MHz

- 1.35 DMIPS/MHz

- Gate count: 26 kgates

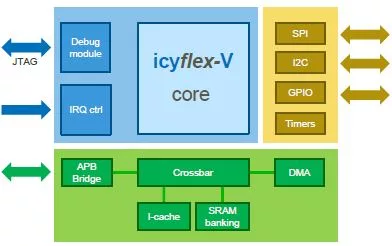

Block Diagram

Benefits

- e.g. Implementation in TSMC 55 nm LP HVT

- Core only area : 0.056 mm2

- Max. frequency (SS corner, 1.08 V, -40 °C) : 120 MHz

- Power consumption 18 uW/MHz (TT corner, 1.2 V, 25 °C)

Applications

- IOT

- Wearables

- Mixed-signal applications

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Low-power 32-bit RISC-V processor?

Low-power 32-bit RISC-V processor is a CPU IP core from CSEM listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.