Low power 32-bit processor with secure execution capability

E803 utilizes a 3-stage sequential pipeline to achieve an optimized balance between performance and cost.

Overview

E803 utilizes a 3-stage sequential pipeline to achieve an optimized balance between performance and cost. It can be equipped with secure execution technology to enhance system security. It is suitable for application fields that are sensitive to cost and power consumption and have certain requirements on performance, such as MCU and wireless connectivity.

Key features

- Instruction set: T-Head ISA (32-bit/16-bit variable-length instruction set);

- Pipeline: 3-stage;

- General register: 16 32-bit GPRs;

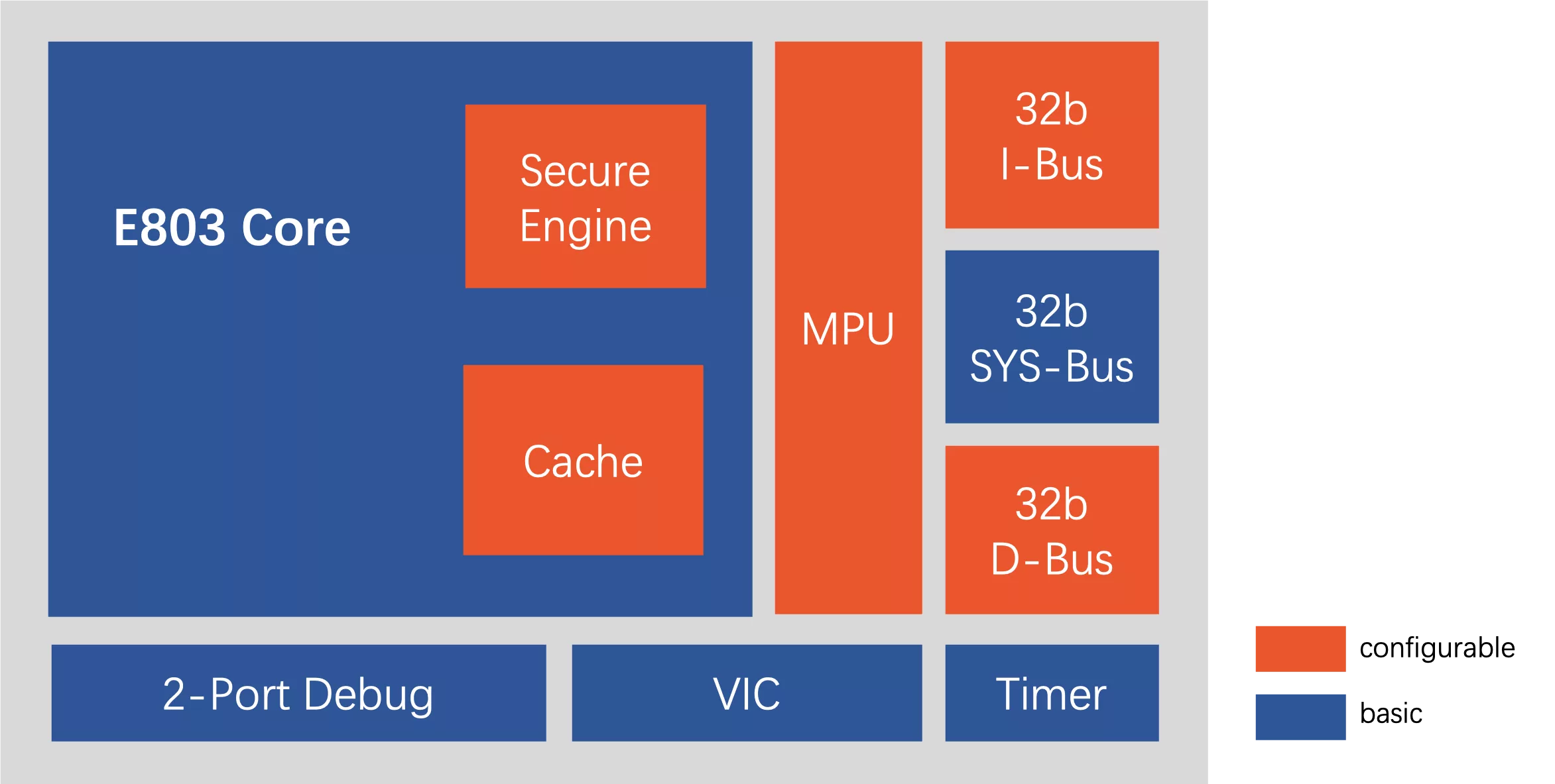

- Bus interface: Tri-bus (instruction bus + data bus + system bus) ;

- Memory protection: 0 to 8 optional protection zones;

- Tight coupling IP: Interrupt controller and timer;

- Multiplier: Single-cycle multiplier;

- Secure execution technology: Resists any hardware and software attacks, and increases system security;

- Low-power cache: Reduces system memory access latency, and improves memory efficiency;

- Interrupt response acceleration technology: Enhances the system's real-time performance to allow users to quickly enter the corresponding service program;

- -time performance to allow users to quickly enter the corresponding service program

- Speculative memory access technology: Reduce branch processing overheads, and improve access efficiency.

Block Diagram

Applications

- Wireless Connectivity;

- Industrial Control.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Low power 32-bit processor with secure execution capability?

Low power 32-bit processor with secure execution capability is a CPU IP core from T-Head listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.