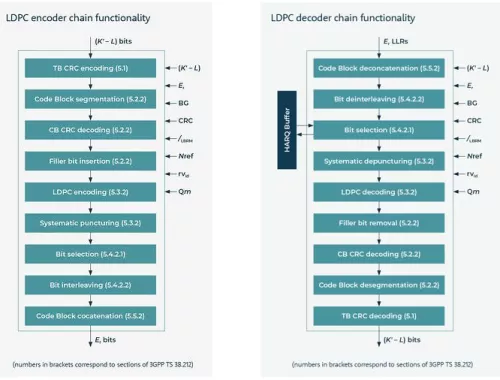

Our LDPC encoding and decoding IP for the 3GPP New Radio uplink and downlink data channel includes the entire processing chain, to provide quick and easy integration and minimize the amount of extra work needed.

The LDPC core uses novel layer belief propagation schedules with early termination, in order to achieve compromise-free error correction performance with high hardware efficiency.

LDPC Encoder / Decoder for 3GPP 5G NR

Overview

Key Features

- Fully compliant with the 3GPP NR standard for PDSCH, PUSCH. Supports the full range of uncoded and encoded block sizes

- Implements the entire LDPC encoding and decoding chain in 3GPP TS38.212

- High error correction performance from LDPC decoder core

- Tightly integrates the components in the chain to reduce area usage and latency

- Simple interface, quick to integrate – all parameters are internally calculated

- FPGA support for Xilinx, Intel and Achronix

- Optimized for ASIC process

- Optimized software solution on Intel Architecture and AVX512 acceleration

- Matlab and C Models available

- Configurable parameters for power & performance optimization

- Scalable design

- Standard AXI interfaces

Benefits

- Encoder

- Transport Block CRC encoding

- Code block segmentation

- CRC encoding

- LDPC encoding (basegraph 1 and 2, all Z-values)

- Rate matching (incl. repetition)

- Bit-level interleaver

- Filler bits insertion/removal

- Code block concatenation

- Decoder

- Transport Block CRC decoding

- Code block de-segmentation

- CRC decoding

- LDPC decoding (basegraph 1 and 2, all Z-values)

- HARQ combining

- Filler bits insertion/removal

- Inverse Rate matching (incl. repetition)

- Bit-level de-interleaver

- Soft-output interface (optional)

- Re-encoded output stream (optional)

- Code block de-concatenation

Block Diagram

Applications

- The LDPC encoding and decoding chains are the building blocks that furthers usage in a variety of applications. Our flexible IP can be used in a wide range of applications ranging from ASICs for dedicated implementations through lookaside accelerators for cloud RAN and software implementations.

Deliverables

- RTL

- C/Matlab Models

- Test bench