JESD204C Transmitter IIP

JESD204C interface provides full support for the JESD204C synchronous serial interface,compatible with JESD204C version specifica…

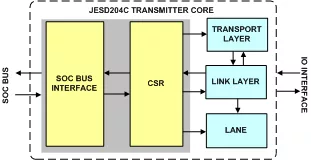

Overview

JESD204C interface provides full support for the JESD204C synchronous serial interface,compatible with JESD204C version specification. Through its compatibility,itprovides a simple interface to a wide range of low-cost devices. JESD204C Transmitter IIP is proven in FPGA environment. The host interface of the JESD204C can besimple interface or can be AHB,AHB-Lite,APB,AXI,AXI-Lite,Tilelink,OCP,VCI,Avalon,PLB,Wishbone or Custom protocol.

JESD204C Transmitter IIP is supported natively in Verilog and VHDL

Key features

- Compliant with JESD204 specification JESD204A, JESD204B.01 and JESD204C.

- Full JESD204C transmit functionality.

- Supports data rate upto 32 Gbps.

- Supports programmable clock frequency up to 32 GHz.

- Supports up to Subclass 0, 1, 2.

- Supports up to Version A, B and C.

- Supports 1 to 8 lanes.

- Supports 1 to 8 converters per transmitter.

- Supports frame sizes of 1,2,4,8 and 16 octets per frame.

- Supports HD-mode.

- Supports 1 to 32 bit data width per converter.

- Supports CF = 0 and 1 control words per frame clock period per link.

- Supports 0 to 3 control bits per sample.

- Supports 1 to 8 samples per converter.

- Supports 1 to 32 frames per multiframe.

- Supports 4, 8, 12, 16, 20, 24, 28 and 32 bits per sample.

- Supports 0 to 15 bank ID – extension to DID.

- Supports 0 to 255 device identification number.

- Supports 0 to 7 lane identification number.

- Supports 8b/10b encoding.

- Supports 64b/66b encoding.

- Supports 64b/80b encoding.

- Supports Forward Error Correction (FEC) and cyclic redundancy checks (CRC).

- Supports single block, Multi block and extended multi block.

- Supports different Serdes interfaces 10,20,40,60 bits and custom bits per lane.

- Continuous sequence of a scrambled jitter pattern (JSPAT) and modified random pattern (modified RPAT).

- Continuous sequence of either /D21.5/ or /K28.5/ characters for code group synchronization.

- Repeated transmission of a lane alignment sequence, preceded by a code group synchronization sequence.

- Scrambler can be enabled or disabled.

- MCDA-ML (Multiple-Converter Device Alignment, Multiple-Lanes) device supported.

Block Diagram

Benefits

- Single site license option is provided to companies designing in a single site.

- Multi sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs,license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

What’s Included?

- The JESD204C Transmitter interface is available in Source and netlist products.

- The Source product is delivered in verilog. If needed VHDL, SystemC code can also be provided.

- Easy to use Verilog Test Environment with Verilog Testcases.

- Lint, CDC, Synthesis, Simulation Scripts with waiver files.

- IP-XACT RDL generated address map.

- Firmware code and Linux driver package.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

What is JESD204C? A quick glance at the standard

Frequently asked questions about JESD204 IP cores

What is JESD204C Transmitter IIP?

JESD204C Transmitter IIP is a JESD204 IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.