ISDB-S3 demodulator

The CMS0071 ISDB-S3 Demodulator is a high-performance (A)PSK demodulator core intended for ARIB STD-B44 ISDB-S3 wide band digital…

Overview

The CMS0071 ISDB-S3 Demodulator is a high-performance (A)PSK demodulator core intended for ARIB STD-B44 ISDB-S3 advanced wide band digital satellite standard.

Operating symbol rate is programmed from a register and extends from approximately 40% of the master clock frequency down to an arbitrary low rate that is set through synthesis options. The range would normally be dictated by the application and, in particular, the phase noise characteristics of the radio system.

Carrier acquisition is performed in several stages starting with a coarse, stepped search. The search range and step size are programmed through registers and can be set to accommodate an arbitrary offset (within the sample rate bandwidth).

Payload symbols are output as soft decisions after descrambling and the recovery of carrier phase, symbol timing and gain.

The CMS0071 is provided with a baseband I/Q radio interface compatible with zero-IF and near-zero-IF tuner modules. The interface performs automatic compensation of DC offsets and quadrature imbalances (phase and amplitude).

Tuner Rx gain control is provided through PDM output RxAGC. Further stages of gain control are implemented digitally within the demodulator.

The Decimation Filter stage suppresses wideband interference and restricts the sample rate bandwidth prior to matched (RRC) channel filtering and timing recovery. The combined response of the Decimation and Channel Filters allows the CMS0071 to tolerate up to +10dBc of adjacent channel interference at any supported symbol rate.

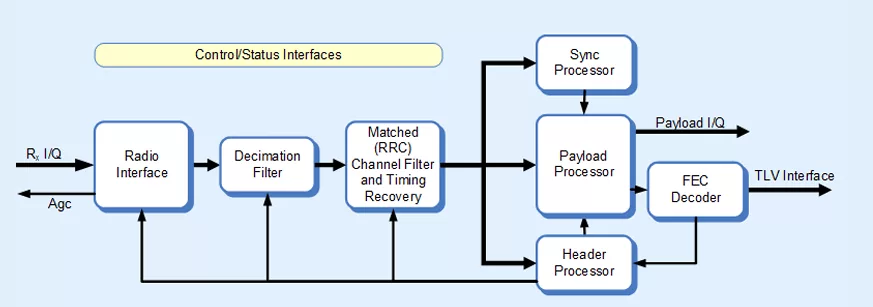

Three dedicated processors at the output of the Channel Filter handle the ISDB-S3 specific demodulation functions:

Sync Processor. This is responsible for the recovery of initial Physical Layer (PL) frame and slot synchronisation from the Start of Frame (SOF) sequences at the start of each slot.

Header Processor. This is responsible for configuring the Payload Processor according to the decoded TMCC signalling information which defines the slot configuration, modulation format and FEC code rate of the slots within the ISDB-S3 frame structure.

Payload Processor. This delivers soft output symbols (unsliced constellation samples) to the LDPC Decoder after carrier phase correction, gain normalisation and PL descrambling.

Register Configuration

Static configuration and status monitoring is performed through a bank of registers. This would typically be driven from a processor interface connected to a CPU that is embedded on the same device or located off-chip.

Parameters accessible through this interface include:

- Nominal symbol and input carrier frequencies;

- Window and step sizes for the coarse carrier search;

- AGC and PLL configuration and status;

- Estimated signal-to-noise ratio (CNIR).

Important synchronisation events such as the acquisition of symbol timing lock or PL frame sync are signalled through the SyncEvents output. Some or all of these signals would typically be connected to the processor interface as sources of interrupt but might otherwise be polled as status indicators.

The Channel and Decimation Filters use hard-wired FIR filter coefficients that are generated during synthesis. FPGA platforms employing more than one Channel Filter configuration would normally store a different netlist for each filter used.

The option of programmable coefficients is available for ASIC and high-end FPGA platforms that have adequate (multiplier) resources.

Full details of the register interface are provided in the CMS0071 IP Guide document.

Key features

- Fully compliant with ARIB STD-B44.

- Automatic slot and frame acquisition using received header and TMCC signalling information.

- BPSK, QPSK, 8-PSK, 16-APSK and 32-APSK supported.

- Support for an arbitrary range of symbol rates up to 40% of the master clock frequency.

- Two-stage, stepped carrier search provides wide acquisition range.

- Integrated LDPC and TMCC decoding.

- Baseband I/Q radio interface incorporating compensation for DC offset and quadrature imbalances.

- Pilot-assisted carrier tracking ensures robust performance in the presence of high levels of phase noise.

- Physical layer sync acquisition and maintenance at –2dB SNR (Es/N0).

- Digital decimation and channel filters reject up to +10dBc of adjacent channel interference.

- Fully-digital carrier and clock recovery circuits eliminate the need for an external VCXO.

- Supplied as a protected bitstream or netlist (Megacore® for Altera® FPGA targets).

Block Diagram

Applications

- ASICs for digital satellite TV reception.

- High-end interactive satellite terminals.

- Test, measurement and broadcast monitoring equipment.

- Multi-standard, adaptable (software defined) receivers.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Our expertise is primarily in the gate- and power-efficient implementation of physical-layer (PHY) functions such as: modulation, demodulation, equalisation and channel coding but our experience encompasses all of the major elements of a modern baseband 'core' including the medium access control (MAC), voiceband DSP, mixed-signal interfaces, and embedded Cpu and software.

Our services are provided on a turnkey basis or as part of a support package attached to our licenced IP or tool products.

Commsonic's customers are typically semiconductor vendors and manufacturers of communications equipment that require leading-edge, Standards-based or proprietary PHY solutions but lack the internal resources or skills necessary to deliver projects against aggressive deadlines.

Learn more about Modulation Demodulation IP core

Three Major Inflection Points for Sourcing Bluetooth Intellectual Property

Part 2: Opening the 5G Radio Interface

An Integrated, Tunable RF Filter: an Enabler for Reconfigurable Front-Ends

Design considerations for integrated CMOS receivers

Silicon IP for Programmable Baseband Processing

Frequently asked questions about Modulation and Demodulation IP cores

What is ISDB-S3 demodulator?

ISDB-S3 demodulator is a Modulation Demodulation IP core from Commsonic Ltd listed on Semi IP Hub.

How should engineers evaluate this Modulation Demodulation?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Modulation Demodulation IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.