Learn more about Interlaken IP core

Protocol selection plays a crucial role in such high-speed environment directly affecting performance through factors like encoding efficiency and error resiliency.

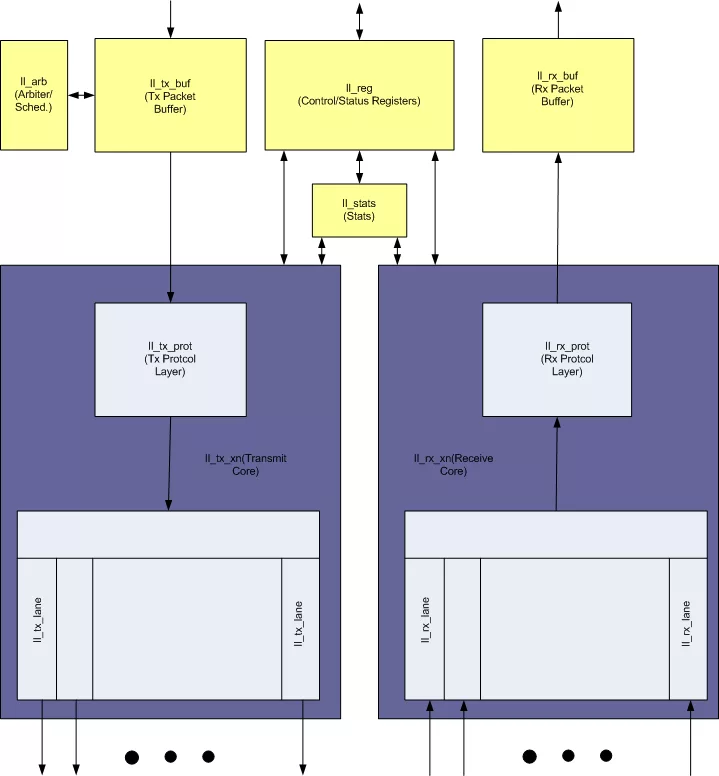

The Interlaken protocol is an advanced interconnect technology that effectively addresses the architecture and design requirements of AI chips. It provides high bandwidth through multi-gigabit-per-second lanes, facilitating the handling of large data volumes and sustaining high computational throughput.

As data consumption grows and chip designs evolve to meet this demand, Interlaken is the ideal high-speed chip-to-chip interface with efficiency, reliability and scalability.

The future of networking is about higher bandwidth and lower power. More and more applications, such as video, continue to drive the bandwidth demands placed on networking equipment. At the same time, networking equipment must deliver these higher bandwidths without a dramatic increase in power consumption.

At Silicon Creations, we have developed a power and area optimized, flexible and programmable PMA (Physical Medium Attachment) architecture that can be reliably ported to different process nodes and scaled across protocol generations as data rates increase. It is called the Multi-Protocol PMA, or MP-PMA for short.

The need for higher and higher bandwidth is growing, which is pushing the SerDes speed to 56G and beyond. The next generation of networking devices are already pushing for 400G bandwidth and above. Both the OIF CEI-56G and IEEE working groups have ratified the 56G specifications, and for higher speed SerDes, PAM4 signaling is the way forward.