Intelligent Sensor and Power Management Design Platform

The IQonIC Works ISP is an integrated ASIC design platform for low power analog/mixed signal ASICs for IoT, Smart Home, Healthcar…

Overview

The IQonIC Works ISP is an integrated ASIC design platform for low power analog/mixed signal ASICs for IoT, Smart Home, Healthcare, Wearables, and Industrial applications that will simplify, streamline and reduce the cost for new ASIC designs.

The IQonIC Works ISP includes:

- Integrated ASIC reference architecture and design, and a library of analog and digital design and verification IP.

- Complete SDK, including SW drivers for all HW interfaces and functions and sensor calibration tools.

- Virtual Development Environment for application SW development, validation and safety certification, with full simulation capability for application development with better, simpler and more comprehensive debugging features.

Key features

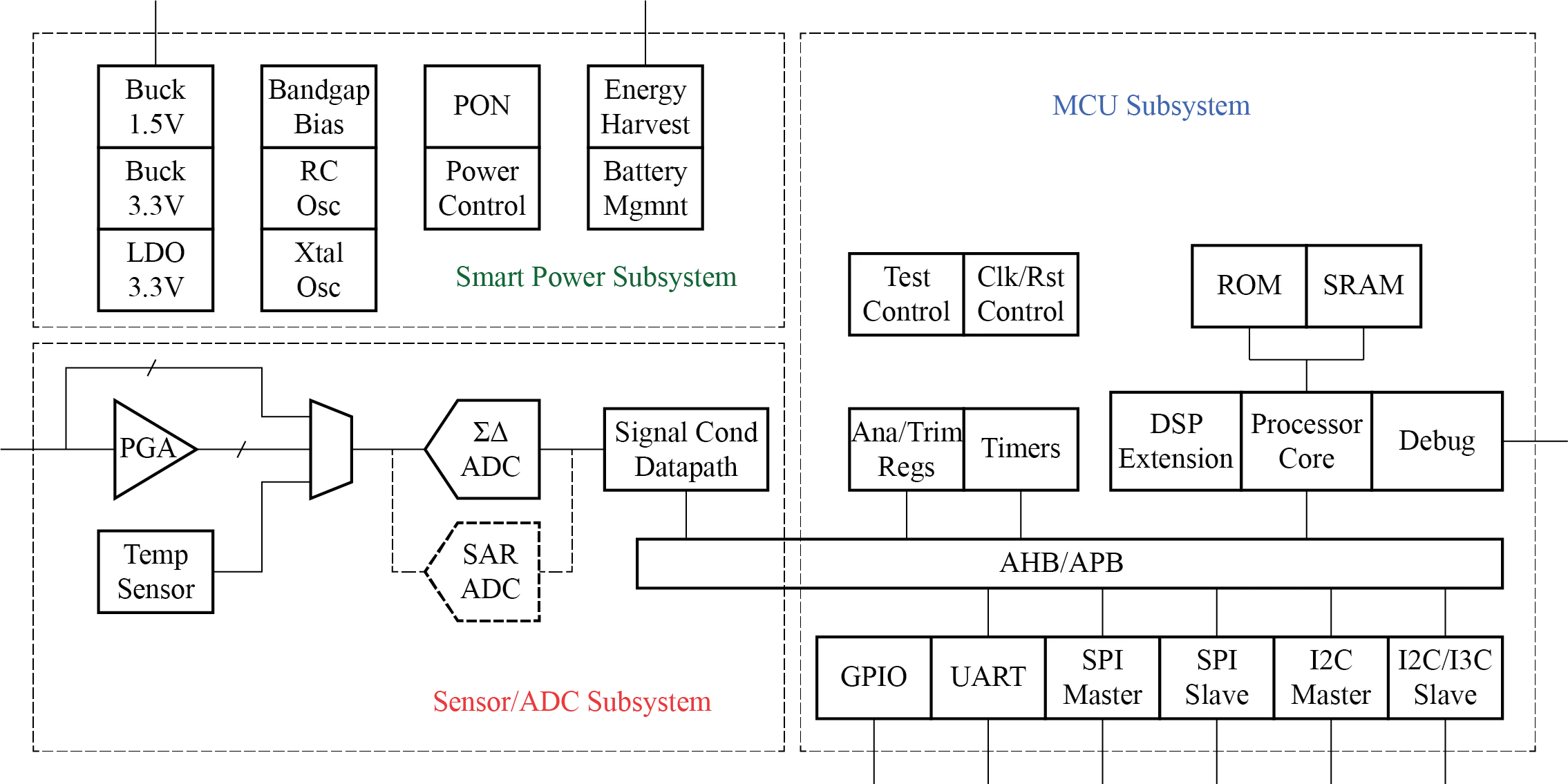

- Smart Power Subsystem

- Fault detection & on/off control: monitors battery and power supply levels, turns off external battery FET in fault condition, turns system on/off based on power button

- Buck regulator for ASIC I/O and external components, extends battery life

- LDO Linear regulator for low-noise analog supply

- Buck regulator for ASIC digital core in operational mode

- Power control: manages operational/standby state and controls regulators

- 900MHz RF Energy Harvester and Rectifier module

- RC/Xtal oscillator: Clock oscillator for ASIC, low-frequency RC for standby

- Power-on reset: Reset system when power applied or after fault cleared

- Ext clock/reset buffer: Provides buffered clock and reset signals to external components

- Bandgap reference: Provides references for regulators, oscillator, DAC, and other circuits

- JTAG TAP: Digital test access point

- Analog test control: Controls test mode and selects analog test points to drive test pads

- Sensor AFE

- SAR ADC for higher speed conversion

- Temperature Sensor

- Three input channel PGAs

- Programmable Signal Conditioning DSP

- MCU Subsystem

- MCU core: RISC-V, ARM or ColdFire (or ASTC-8051 if memory and performance requirements allow)

- Debug control: Register/memory access, run/step, trace, etc, accessed through JTAG or SMBus

- Watchdog timer: For firmware time-out reset

- Tick timer: For firmware task scheduling

- Interrupt controller: Manages interrupts from I/O blocks

- Firmware flash: For code storage, loaded at product assembly, field upgradeable

- Data SRAM: For firmware data

- Signal SRAM: For DSP data to/from external codec, to/from DSP data path, and accessible by MCU core

- DSP data path: Co-processor for MCU for DSP operations

- DMA controller: Transfers data between I/O blocks, DSP data path and signal SRAM

- SPI, I2C master and slave interfaces

- I3C Slave interface

- GPIO

Block Diagram

Benefits

- By key benefit of the IQonIC Works ISP design platform is that provides a complete ASIC design solution, not peacemeal IP blocks, but the entire range of core analog and digital design blocks required to design and implement an edge based ASIC application. All ISP IP blocks have been designed, integrated and verified together in a reference ASIC architecture and design platform for rapid deployment to an ASIC project and for rapid ASIC design as an ISP ASIC derivative. From the IQonIC Works ISP platform to a customer application specific ASIC requires only the addtion of application specific IP and a custom derivative integration.

- Together with a virtual prototyping flow for hardware and software development and verification, and a streamlined flow for deployment to an ASIC project, the IQonIC Works ISP provides a very fast path for design from application specific requirements to a new ASIC.

- ASTC enables a new ASIC project to be executed within the cost budgets and time lines of an ASIC derivative project.

Applications

- The IQonIC Works ISP design platform is targeted for edge based embedded applications, i.e. localized intelligent sensing for monitoring, processing, and control, supporting both ASIC- or FPGA-based implementations, including for

- IoT Monitoring and Control

- Wearables

- Healthcare Patient Monitoring and Tracking

- Consumer Electronics

- Industrial Automation

- Home Automation

What’s Included?

- The following list of deliverables are included:

- Datasheet

- ISP Virtual Platform and baseline SW drivers

- Platform and module RTL

- Top level and module schematics

- Digital and Chip level AMS verification environment and test cases

- Module Test Suites

- Integration Guide

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 130nm | BCD | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Mixed Signal Subsystem IP core

Mixed Signal Design & Verification Methodology for Complex SoCs

Systematic approach to verification of a mixed signal IP - HSIC PHY case study

Customized PMICs with OTP in automotive and IoT

Effective Optimization of Power Management Architectures through Four standard "Interfaces for the Distribution of Power"

How to specify and integrate successfully a measurement analog front-end including its power computation engine in an energy metering IC

Frequently asked questions about Mixed-Signal Subsystem IP cores

What is Intelligent Sensor and Power Management Design Platform?

Intelligent Sensor and Power Management Design Platform is a Mixed Signal Subsystem IP core from IQonIC Works listed on Semi IP Hub. It is listed with support for globalfoundries Silicon Proven.

How should engineers evaluate this Mixed Signal Subsystem?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mixed Signal Subsystem IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.