HW/SW interface foundation for design innovation

It is typical for the HW/SW interface (HSI) of a system-on-chip to grow exponentially in complexity with each new generation.

Overview

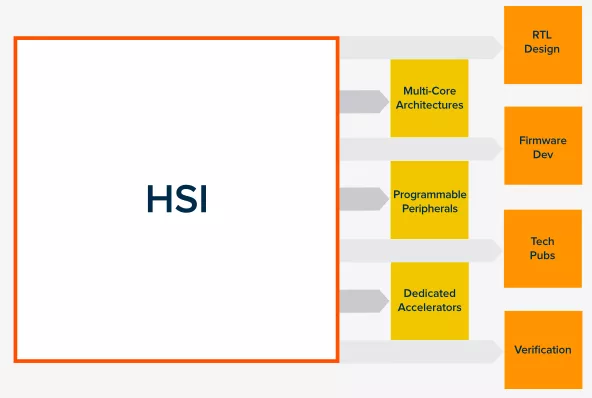

It is typical for the HW/SW interface (HSI) of a system-on-chip to grow exponentially in complexity with each new generation. The HSI database has become an essential design resource used by architects, RTL designers, verification engineers, software developers, and technical writers. Each discipline requires access to the same HSI information, albeit in a specific format, to satisfy its required deliverables. Given this exponential increase in complexity and the need for better communication between the different groups, Arteris presents CSRCompiler and the CSRSpec language as the winning methodology to build the HIS foundation correctly.

CSRCompiler automates HSI design, verification, firmware, and documentation, providing multi-language support without the need for additional scripting. The method supports an agile design process to ensure best practices and early engagement by the entire design team by collaboratively managing the design from a single source specification. It gives a complete, correct, and up-to-date register design ecosystem, turning address map sharing into a smooth and integrated process, and preventing design mistakes during address map deployment.

Key features

- Various Input Formats:

- CSRSpec Language

- SystemRDL

- IP-XACT

- CMSIS-SVD

- Excel Spreadsheets

- VMM RALF

- Legacy Input Languages

- Various Output Formats: Synthesizable RTL: CSRCompiler generates the synthesizable Verrilog and VHDL code for configuration, status, interrupts, masks, counters, and other memory map registers. The synthesizable Verilog code for standard configuration registers can jump-start your design. Synthesizable standard bus interfaces, AMBA, Avalon, OCP-IP and Wishbone aid in IP integration for multi-core and embedded architectures.

- Dynamic Html Web Pages: CSRCompiler automatically generates the HTML interactive view for browsing the entire design.

- Headers for firmware: CSRCompiler builds the headers for firmware code. Its single-source environment eliminates the chance of typos and missing parameters.

- Data Structures: CSRCompiler generates the SystemVerilog, C/C++ and Perl data structures to jump-start system and unit testing of memory map registers. It also supports UVM, VMM and OVM for design verification. IP-XACT XML is provided for interchange. The registers are specified once, and all the views are generated by CSRCompiler ensuring that they are accurate as the design evolves.

- Internal And Customer Documentation: Formatted documentation views provide a clean handoff from design to technical publications. CSRCompiler’s single source eliminates the risk of “stale specifications”. Word, Framemaker and DocBook XML are all supported.

- Extensive Error/Syntax Checking: With over 1,000 functional, behavioral, syntactic, and semantic error checks, CSCompiler performs a strict lexical analysis, parse tree evaluation, and semantic check that extends beyond standards to ensure the address map is self-consistent and will allow the generation of valid RTL.

- Advanced Features: Registers broadcast/alias and virtual registers support, wide memories and atomic access support, industry-standard buses support, field compare, back door path mapping, coverage bins, parity checks.

Block Diagram

Benefits

- Agile Design Process: Ensure best practices and early engagement of the entire design team

- Multi-Language Support: No need for additional custom scripting or manual post-processing

- Identify IP Issues: Ensure clean import of third-party IP or internal legacy data

- Easy Specification Adjustment: Very fast iteration with updated information across design teams ensuring data consistency

- Efficient collaboration: Design, verification, software, and documentation integrated with a single-source specification

- Highly configurable: With over 200 unique properties and 6,000 register behavior combinations.

- Highest Capacity: Specify and compile over 5 million registers

- Highest Quality RTL: Over 1,000 functional, behavioral, syntactic, and semantic error checks

- Fastest Performance: Generate 100,000 registers in seconds

- Shorten time to market: Right the first time with a correct by construction process thanks to the checkers

- Auto-generation of the outputs from the CSRSpec.

Applications

- Register Management of large-scale SoC designs across all market segments.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about System Controller IP core

Low Power Asynchronous Processor With Cordic Co-Processor

Automation in IP based SoC development: Case study of a media processor subsystem

DDR2 Signal Integrity

Extreme partitioning

Reconfiguring Design -> Reconfiguring for broadband access

Frequently asked questions about system controller IP cores

What is HW/SW interface foundation for design innovation?

HW/SW interface foundation for design innovation is a System Controller IP core from Arteris listed on Semi IP Hub.

How should engineers evaluate this System Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this System Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.