High-Speed LVDS (SERDES) Transceiver

The LVDS_SERDES IP Core is a high-speed LVDS transmitter / receiver pair suitable for a wide range of serial interface applicatio…

Overview

The LVDS_SERDES IP Core is a high-speed LVDS transmitter / receiver pair suitable for a wide range of serial interface applications. The design is comprised of an independent transmitter and receiver that may be used separately or together as a single transceiver.

The transceiver can accept parallel data widths of up to 128-bits and features a user-defined multiplexer ratio. By modifying the generic parameters, dw, ratio, duty, skew, lanes and direction, the transceiver can be made compatible with a wide range of third-party LVDS devices such as those from National Semiconductor®, TI®, Thine® and Maxim®.

In total, the transceiver can support up to 8 serial data lanes - each data lane typically handling rates of between 500 Mbits/s and 1Gbits/s. The maximum data rate attained will be dependent on a wide range of factors such as: cable type, cable length, board layout, and the specification of the LVDS buffers. As a general rule, data rates of 350 Mbits/s per lane can be easily achieved on even the most basic FPGA platforms.

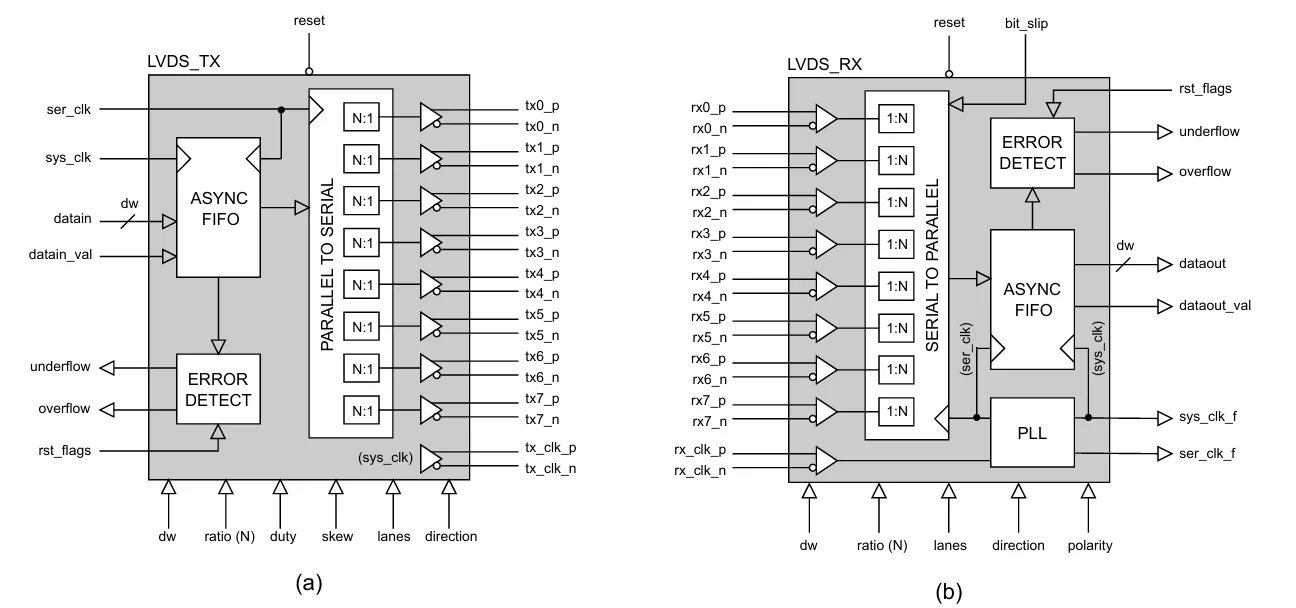

In addition to the 8 data lanes, a single clock lane is provided for synchronizing the data between the transmitter and receiver. Figure 1 shows the basic architecture of the transmitter and receiver pair. The following sections explain the transmitter and receiver functionality in more detail.

Key features

- Technology independent soft IP Core for FPGA, SoC and ASIC

- Supplied as human readable VHDL (or Verilog) source code

- Separate LVDS Transmitter / Receiver (SERDES) pair

- Up to 8 serial LVDS data lanes + LVDS clock

- Fully configurable clocking

- Generic parallel data width up to 128 bits wide

- Generic parallel-to-serial mux ratio up to 16:1

- Data rates of up to 1 Gbits per lane

- Integrated asynchronous FIFOs with underflow / overflow detection

- Bitwise data alignment at the receiver

- No receiver source clock required

- Compatible with a wide range of industry standard protocols including: Channel Link®, Camera Link®, FPD Link®, FlatLink® etc.

- Robust and simple to implement using cheap twisted pair cable (e.g. Cat 5 Ethernet)

Block Diagram

Applications

- High bandwidth SERDES interfaces

- Serialization of wide buses e.g. 'virtual' ribbon cable

- Direct replacement for many commercial LVDS / SERDES ICs

- Data streaming interfaces over cable or twisted pair over longer distances

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is High-Speed LVDS (SERDES) Transceiver?

High-Speed LVDS (SERDES) Transceiver is a Single-Protocol PHY IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.