R807 utilizes an 8-stage pipeline and dual-issue out-of-order architecture. In addition to the cache, it implements tightly-coupled memory (TCM), a low-latency peripheral quick access interface, rapid interrupt response and memory ECC check. It is suitable for application fields requiring high real-time performance and reliability, such as SSD's and industrial control.

High-performance 32-bit processor for real-time control

Overview

Key Features

- Instruction set: T-head ISA (32-bit/16-bit variable-length instruction set);

- Pipeline: 8-stage;

- Microarchitecture: Dual-issue (superscalar), out-of-order;

- General register: 32 32-bit GPRs;

- Cache: I-Cache: 8 KB/16 KB/32 KB/64 KB (size options); D-Cache: 8 KB/16 KB/32 KB/64 KB (size options);

- Tightly-coupled memory: I-TCM: 4 KB to 1 MB (size options); D-TCM: 4 KB to 1 MB (size options);

- Tightly-coupled memory slave interface: Supports an independent TCM slave interface;

- Bus interface: Dual bus (system bus and peripheral bus);

- Peripheral quick access interface: Dedicated quick peripheral access interface;

- Memory protection: 0 to 16 optional protection zones;

- ECC check: Both Cache and TCM support ECC check;

- Floating point engine: Supports single and double precision floating point operations;

- Low-latency tightly-coupled memory: Provides deterministic access to instructions and data to improve real-time performance of the system;

- D-TCM Parallel access blocking: Supports parallel execution of CPU data processing and DMA data handling;

- Peripheral quick access interface: Optimizes peripheral access latency and supporting concurrent bus transmission for peripheral access;

- Rapid interrupt response: Interrupts the execution of long-delay instructions and immediately responds to interruptions, improving the real-time performance of interrupt response;

- Reliability design: Supports ECC validation and error correction of Cache/ECC.

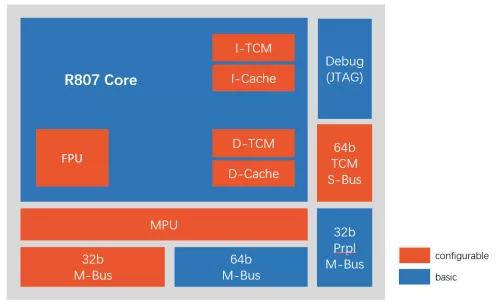

Block Diagram

Applications

- Industrial Control

Technical Specifications

Short description

High-performance 32-bit processor for real-time control

Vendor

Vendor Name