HBM2/2E Memory Controller Core

The HBM2E memory controller IP is designed for use in applications requiring high memory throughput including performance-intensi…

Overview

The HBM2E memory controller IP is designed for use in applications requiring high memory throughput including performance-intensive applications in AI, HPC and graphics.

The HBM2E Interface Subsystem

HBM2E is a high-performance memory that features reduced power consumption and a small form factor. It combines a 2.5D/3D architecture with a 1024-bit wide interface operating at a lower clock speed (as compared to GDDR6) to deliver higher overall throughput at a higher bandwidth-per-watt efficiency for AI/ML and HPC applications.

The HBM2E controller supports both HBM2 and HBM2E devices with data rates of up to 3.6 Gbps per data pin. It supports all standard channel densities including 4, 6, 8, 12, 16 and 24 Gb. The controller maximizes memory bandwidth and minimizes latency via Look-Ahead command processing. The core is DFI compatible (with extensions added for HBM2E) and supports AXI or native interface to user logic.

The HBM2E controller is fully compliant with the JEDEC HBM2E JESD235 standard. It supports data rates up to 3.6 Gbps per data pin. The interface features 8 independent channels, each containing 128 bits for a total data width of 1024 bits. The resulting bandwidth is 461 GB/s per HBM2E memory device containing 2, 4, 8 or 12 3D-stacked DRAM.

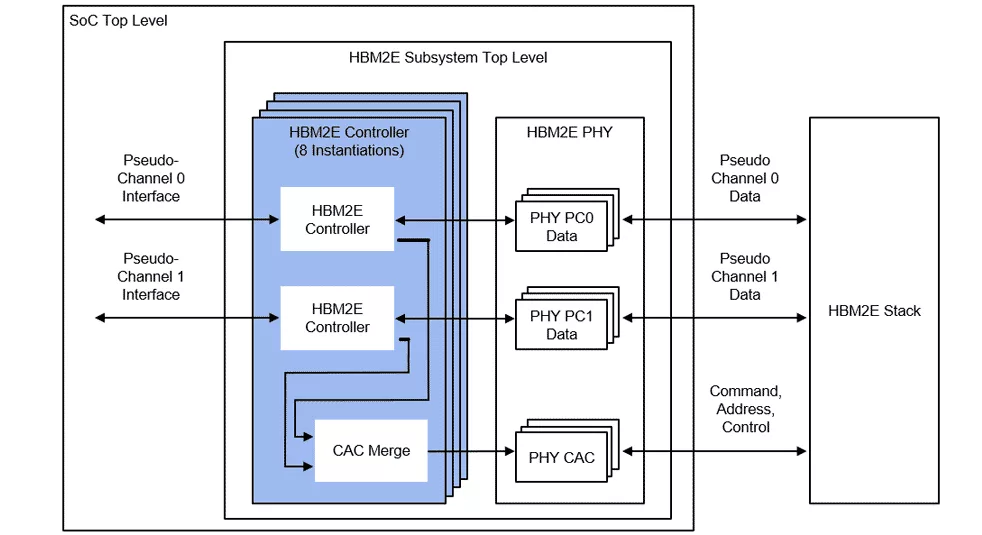

The HBM2E controller together with the customer’s choice of PHY comprise a complete HBM2E memory interface subsystem.

Key features

- Supports HBM2E and HBM2 devices

- Supports all standard HBM2/2E channel densities (4, 6, 8, 12, 16, 24 Gb)

- Supports data rates of up to 3.6 Gbps/pin

- Can handle two pseudo-channels with one controller or independently with two controllers

- Queue-based interface optimizes performance and throughput

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

- Achieves high clock rates with minimal routing constraints

- Full run-time configurable timing parameters and memory settings

- DFI compatible (with extensions added for HBM2)

- Full set of Add-on cores available

- Supports AXI or native interface to user logic

- Support for HBM2/2E RAS features

- Built-in hardware -level performance Activity Monitor

- Delivered fully integrated and verified with target PHY

Block Diagram

What’s Included?

- Core (Source Code)

- Testbench (Source Code)

- Complete Documentation

- Expert Technical Support

- Maintenance Updates

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about HBM IP core

HBM4 Elevates AI Training Performance To New Heights

Making Strong Error-Correcting Codes Work Effectively for HBM in AI Inference

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Breaking the HBM Bit Cost Barrier: Domain-Specific ECC for AI Inference Infrastructure

High Bandwidth Memory (HBM) at the AI Crossroads: Customization or Standardization?

Frequently asked questions about HBM Interface IP

What is HBM2/2E Memory Controller Core?

HBM2/2E Memory Controller Core is a HBM IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this HBM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this HBM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.