Hardware RTP Stack for JPEG Stream Encapsulation

Implements a Real Time Transport Protocol (RTP) hardware stack that encapsulates JPEG streams to RTP packets compliant with RFC 2…

Overview

Implements a Real Time Transport Protocol (RTP) hardware stack that encapsulates JPEG streams to RTP packets compliant with RFC 2435.

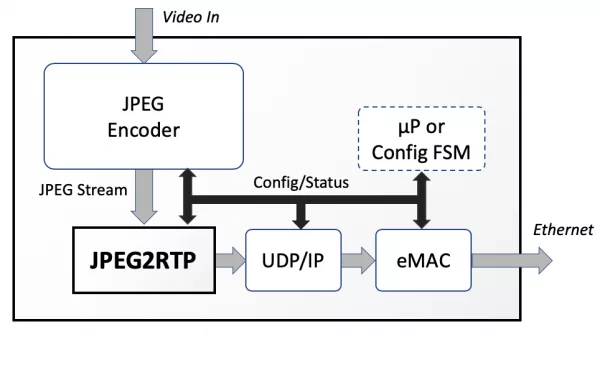

The JPEG2RTP can be directly connected to the output of a JPEG encoder to output RTP packets, which can subsequently be forwarded for UDP/IP or TCP/IP encapsulation. The hardware stack produces complete RTP packets, without the need for any host-processor assistance. Along with CAST’s UDP/IP hardware stack, the JPEG2RTP core is ideal for offloading the demanding task of RTP/UDP/IP encapsulation from a host processor, and enables JPEG video streaming even in processor-less SoC designs.

The core is easy to integrate in systems with or without a host processor. JPEG stream and RTP packet data are input/output via dedicated streaming-capable AXI4-Stream or Avalon-ST interfaces, enabling direct connection to hardware video encoders and hardware stacks for UDP or TCP. Status and control registers are accessible by AXI4-Lite or Avalon-MM interface.

The JPEG2RTP core is available in RTL source or as a targeted FPGA netlist. Platforms integrating the core with JPEG encoder, UDP/IP, and eMAC cores, are also available from CAST, and can enable rapid development of video over IP systems.

The JPEG2RTP core is suitable for a wide variety of systems and devices featuring JPEG video streaming over IP networks. A sample block diagram of such systems is provided above.

Key features

- RTP Encapsulation for JPEG Streams

- Compliant to RFC 2435

- Enables control of RTP packet size

- Run-time programmable maxi-mum stream bytes per RTP packet

- In-band Quantization Table support

- Easier Integration for Faster Development

- Processor-less, standalone operation

- AMBA® - AXI Interfaces

- AXI4-Lite Control/Status register interfaces

- AXI4-Streaming interfaces for packet data

- Avalon Interfaces

- Avalon-MM Control/Status register interfaces

- Avalon-ST interfaces for packet data

- Available pre-integrated with:

- JPEG Encoder cores from CAST

- UDP/IP Hardware Stack from CAST

- Altera, Xilinx, or other third-party eMAC core

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Image Conversion IP core

Nextreme Structured ASICs: An alternative for designing cost-optimized ARM926EJ processor-based embedded systems

Video Messaging for ARM7-based Cellular Chipsets.

Configurable Processors for Video Processing SOCs

Generating High Speed CSI2 Video by an FPGA

Viewpoint: Opportunity to win on different design fronts

Frequently asked questions about image conversion IP cores

What is Hardware RTP Stack for JPEG Stream Encapsulation?

Hardware RTP Stack for JPEG Stream Encapsulation is a Image Conversion IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this Image Conversion?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Image Conversion IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.