Gigabit Ethernet Media Access Controller

Implements an Ethernet Media Access Controller compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specification…

Overview

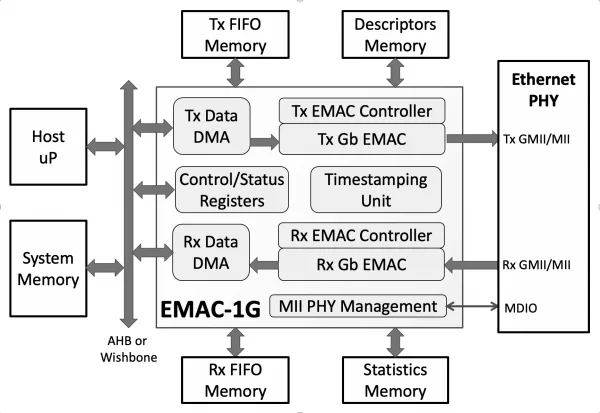

Implements an Ethernet Media Access Controller compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications. The controller provides half- or full-duplex operation, supports jumbo frames, and optionally provides a useful set of statistics counters enabling station management. Furthermore, the core can optionally be configured with a hardware timestamping unit enabling support for the IEEE 1588 precision time protocol (PTP).

A host processor can control the operation of the core via a slave interface that provides access to its control and status registers. The EMAC-1G features two master ports for data transfers, one for transmit and one for receive. The two DMA engines use buffer descriptors to automatically transfer data from local FIFOs to an external shared memory. The core supports 32-bit AMBA/AHB or Wishbone SoC buses; other bus interfaces are available on request.

Integration with an Ethernet PHY is straightforward, as the controller core supports the Media Independent Interface (MII) and the Gigabit Media Independent Interface (GMII) physical layer interface standards.

The EMAC-1G is production proven in ASIC and FPGA technologies.

Key features

- Data Link Layer

- Programmable 10/100 or 1000 Mbps operation

- IEEE 802.3-2002 specification with preamble, start-of-frame delimiter (SFD), and CRC generation and checking

- Full- or half-duplex operation

- 10BASE-T1S, & 100BASE-TI support

- Jumbo frames

- Flexible address filtering

- Extensive statistics counters

- Detection of too long or too short packets, with programmable length limits

- PTP/IEEE 1588 Support (Optional)

- Hardware timestamping unit

- Linux Socket Driver supporting hard-ware or software timestamping

- LinuxPTP application stack supporting a wide range of profiles

- PHY Interfaces

- Media Independent Interface (MII) for 10/100Mbps

- Gigabit Media Independent Interface (GMII) for 1Gbps

- MDIO interface for PHY configuration and management

- Optional Reduced Media Independent Interface (RMII)

- Optional Reduced Gigabit Media Independent Interface (RGMII)

- Optional Serial Gigabit Media Independent Interface (SGMII)

- Host Interface

- AMBA/AHB or Wishbone 32-bit slave for status and control

- One interrupt line per Tx and Rx.

- Clock switch control port (10/100 or 1000 Mbps)

- DMA Controller

- AMBA/AHB or Wishbone 32-bit master separate for Tx and Rx

- Big or little-endian data byte ordering

- With some Scatter/Gather capabilities

- Configurable number of Buffer-Descriptors

- Safety Enhanced Version (Optional)

- ISO 26262 ASIL Ready

- Implements ECC for inner modules protection

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Gigabit Ethernet Media Access Controller?

Gigabit Ethernet Media Access Controller is a Ethernet IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.