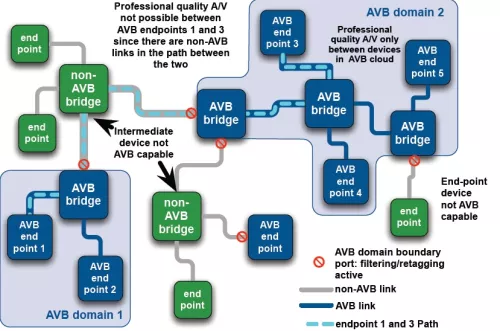

The Arasan Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard. In addition, the Gigabit Ethernet MAC with AVB (Audio Video Bridging) supports the technical standards developed by the (IEEE) Audio Video Bridging Task Group of the IEEE 802.1 standards committee. An AVB MAC supports protocols that differ from standard Ethernet protocols in four significant ways:

- Precise synchronization,

- Traffic shaping for media streams,

- Admission controls, and

- Identification of non-participating devices.

These features permit AVB devices to: a) reserve a portion of network resources through the use of admission control and traffic shaping and b) send and receive new timing-based frames thus enabling support for audio and video applications were synchronization of data streams is important. The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII). It also supports optional Reduced MII (RGMII), and Serial GMII (SGMII).. The Gigabit Ethernet IP is designed for SoC and mobile applications such as integrated networking devices, PCI-Express Ethernet controllers, and Ethernet adapter cards. The Gigabit Ethernet IP supports half-duplex mode at 10/100 Mbps and full-duplex mode at 10/100/1000 Mbps. The Gigabit Ethernet IP core consists of two configurable FIFOs on both transmit and receive sides to handle the application’s latency during frame transmission and reception. A processor bus master and a 32-bit scatter-gather DMA transfer packets between the internal FIFOs and the host memory to enhance system performance. The Gigabit Ethernet IP supports 4-bit MII based 10/100 Mbps PHY and 8-bit GMII based 10/100/1000 Mbps PHY. A MDIO/MDC (Management Data Input/Output and Management Data Clock) management interface provides control and management functions to external PHY devices. The Gigabit Ethernet IP also provides enhanced programmable features for minimizing applications complexity and pre/post message processing. The Gigabit Ethernet IP supports MIB, SNMP, RMON, VLAN Q-Tag frame, and Jumbo frames. It also includes dynamic generation, checking, and stripping of FCS field, automatic pad field insertion, automatic retransmission and detection of collision frames, collision avoidance and handling. Other features of the Gigabit Ethernet IP includes generation and decoding of PAUSE control frames, frame boundary delimitation, frame synchronization, and error detection.

Gigabit Ethernet MAC with AVB

Overview

Key Features

- Fully compliant with IEEE AVB (Audio Video Bridging) Standard

- Full-duplex mode at 10/100/1000 Mbps

- Half-duplex mode at 10/100 Mbps

- Supports IEEE 802.3-2008 compliant MII, RMII, SMII, GMII, RGMII, and SGMII

- Independent 32-bit scatter-gather DMA with big/ little endian operation

- Optional VLAN Q-Tag frame support

- CSMA/CD Protocol for half-duplex mode

- PAUSE frame based flow control in full-duplex mode

- MDIO/MDC management interface

- 802.3 compliant MIB, SNMP, RMON management support

- Configurable transmit and receive FIFOs

- Supports Jumbo frames

- Supports magic packet and Wake-Up frames

- Optional AXI, AHB, PCIe, PCI or custom bus interface

- Variable length Inter Frame Gap (IFG) on back to back frame transmission

- Variable length (3, 5, 7 bytes) preamble generation

- Automatic generation of FCS and PAD

- Option to disable PAD or CRC32

- Option to stop frame retransmission on collisions

- TimeStamps the specified PTP Packets for implementing 1588 Protocol.

- Inter Frame Gap checking

- Preamble detection and stripping

- Flexible address filtering modes and inverse address filtering

- 64-bit hash table to filter multicast addresses

- Promiscuous mode of operation

- Reception of broadcast frames

- Automatic checking the FCS field, runt frames, and data field length

- Detection of MaxFrameLen frames, receive errors

- 32-bit status information on each receive frame

- Identifies PTP Frames (both V1 and/or V2) in L2/ L4 Encapsulation and TimeStamps for implementing 1588 Protocol.

- Software controlled PAUSE control frame generation including multicast and unicast address

- Automatic detection and checking of PAUSE frames

Benefits

- Fully compliant core

- Premier direct support from Arasan IP core designers

- Easy-to-use industry standard test environment

- Unencrypted source code allows easy implementation

- Reuse Methodology Manual guidelines (RMM) compliant verilog code ensured using Spyglass

Block Diagram

Deliverables

- RMM Compliant Synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

Technical Specifications

Maturity

In production

Availability

Now

Related IPs

- 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface

- Gigabit Ethernet MAC with IEEE 1588 PTP Support and AVB for Auto

- 10 Gigabit Ethernet MAC with IEEE 1588 PTP Support and AVB for Auto

- Ethernet PCS IP - Integrates MAC IP to a broad range of PHY and SerDes IP

- Gigabit Ethernet Media Access

- Gigabit Ethernet Transceiver