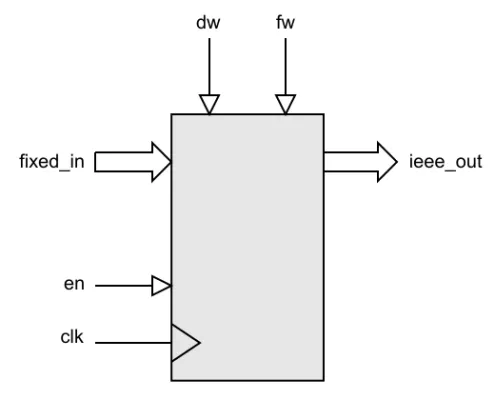

Converts fixed-point numbers to 32-bit floating-point representation. The fixed-point input has a configurable word and fraction width. Floating-point outputs are based on the IEEE 754 standard.

The design features a high-speed, fully pipelined architecture with a 2 clock-cycle latency.

Fixed-point to Floating-point Converter

Overview

Key Features

- Signed fixed-point or integer input

- 32-bit floating-point output

- Configurable word width (up to 32-bits)

- Configurable fraction width (up to 23-bits)

- IEEE 754 compliant

- High-speed fully pipelined architecture

- Only 2 clock-cycles of latency

- FPGA clock rates of 300MHz+

- Low area footprint

Benefits

- Technology independent soft IP Core

- Suitable for FPGA, SoC and ASIC

- Supplied as human-readable source code

- One-time license fee with unlimited use

- Field tested and market proven

- Any custom modification on request

Block Diagram

Deliverables

- VHDL source-code (or Verilog on request)

- Simulation test bench

- Examples and scripts

- Full pdf datasheet

- One-to-one technical support

- One years warranty and maintenance

Technical Specifications

Short description

Fixed-point to Floating-point Converter

Vendor

Vendor Name

Foundry, Node

All

Availability

Immediate