The APS1 from Cortus is a cost effective 32 bit processor core specifically designed to address the needs of engineers wishing to move from traditional 8 bit microcontroller cores.

Designed to have a minimal silicon footprint, very low power consumption and excellent code density, designers upgrading from 8 bit cores, will save silicon area, reduce their code size, increase the autonomy of their battery driven devices and have more processing power to execute their software.

The APS1 is well suited to sensors, home automation, automotive applications, managing I/O and simpler protocols. As a member of the Cortus APS family of processors the APS1 shares the key architectural features of the other processors, with a common toolchain and IDE, bus interface and peripheral set.

The ASP1 is fully upwards compatible with the other APS processors. The modern RISC architecture and careful design ensures that the APS1 can achieve a high maximum clock frequency.

The APS1 has been designed to provide a cost effective and attractive alternative to 8 bit microcontroller cores in many designs.

The 32 bit RISC core is easy to program in high level languages thus reducing software development costs and risk. The clean architecture, peripherals and development environment of the APS1 means that engineers who have previously been developing for 8 bit microcontrollers will rapidly be able to develop efficient applications; leading to quicker application development and reduced software development risk.

The simple, vectored, interrupt structure ensures low latency, real time, response to external events with a minimum of overhead. Up to 27 external user interrupts are supported.

The APS1 is based on the proven APS architecture, ensuring good performance coupled with small silicon footprint, most instructions (including loads and stores) execute in a single cycle due to the 3 pipeline with out-of-order completion. The sophisticated features of this architecture are not found in alternative processors but ensure higher performance, lower power consumption and yet the smallest silicon footprint.

Energy efficient, low cost, 8 bit replacement, 32 bit microcontroller

Overview

Key Features

- Cost Effective 32 bit Core

- Energy Efficient RISC Core

- Ideal 8 bit Replacement

- 64 KBytes of Program

- 64 KBytes of Data

- 3 Stage Pipeline with Out of Order Completion

- 27 External Interrupts

- 2.37 DMIPS/MHz

- Low Power

- Good Code Density

Benefits

- Good performance CPU

- Tiny silicon footprint, less slicon area

- Low Power, longer battery life

- Good Code Density, less Flash memory required

- RTOS support: FreeRTOS, uCLinux, uC/OS II, uC/OSIII, TargetOS

- Full Development Environment

- Optional standard peripherals (counter, timers, watchdog, GPIO, I2C, SPI & UARTs)

- Optional Ethernet 10/100 MAC and USB2.0 Peripheral

- Optional JTAG-Ethernet Debug Solution

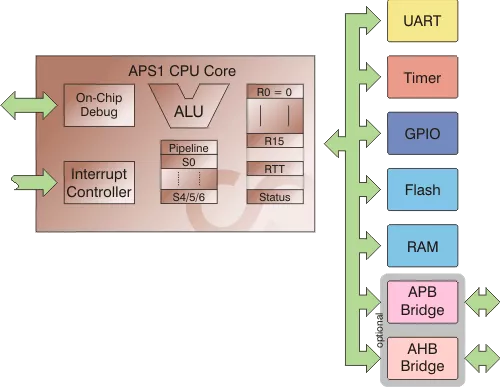

Block Diagram

Applications

- Smart Sensors

- State Machine Replacement

- 8 bit Core Replacement

- Touchscreen Controllers for Mobile Phones and Tablets

Deliverables

- Synthesisable GTECH netlist

- Full Toolchain

- Graphical Development Environment

- Debugger

- Standard Peripherals

- Full Documentation

- Complete Integration Guide

- Supplied as Part of a Design Services Contract

Technical Specifications

Short description

Energy efficient, low cost, 8 bit replacement, 32 bit microcontroller

Vendor

Vendor Name

Foundry, Node

All

Maturity

In Full Production

Availability

Now

Related IPs

- High performance, flexible, 32 bit Energy Efficient Embedded Microcontroller

- Energy efficient, small footprint, 32 bit microcontroller core

- Energy efficient, small footprint, excellent code density, 32 bit microcontroller

- High performance, flexible, extendible 32 bit microcontroller core featuring excellent code density

- Small, Low Power, Energy Efficient 32-bit Microcontroller Processor

- 8 Channel, 12 bit 200K Sample rate ADC - 0.18um G