DVB-S2X Wideband Demodulator

The DVB-S2X Wideband demodulator is a low-complexity high-performance solution that allows for symbol rates of up to 500 MSymb/s …

Overview

The DVB-S2X Wideband demodulator is a low-complexity high-performance solution that allows for symbol rates of up to 500 MSymb/s on state-of-the-art FPGAs. DVB-S2X is the next generation satellite transmission standard which is an extended version of its well-established predecessor DVB-S2. The new specification allows for spectral efficiency gains of up to 50% by offering lower roll-off factors, higher modulations and a finer code rate granularity compared to DVB-S2.

Key features

- Compliant with ETSI EN 302 307-1 V1.4.1 (2014-11) (DVB-S2) and ETSI EN 302 307-2 V1.1.1 (2014-10) (DVB-S2X).

- Supports CCM, ACM and VCM modes

- Support for QPSK up to 256-APSK

- Support for short blocks (16200 bits) and long blocks (64800 bits)

- Optional support for Annex M (time-slicing)

- Output of XFECFRAMEs for further processing by the Creonic DVB-S2X FEC decoder IP core

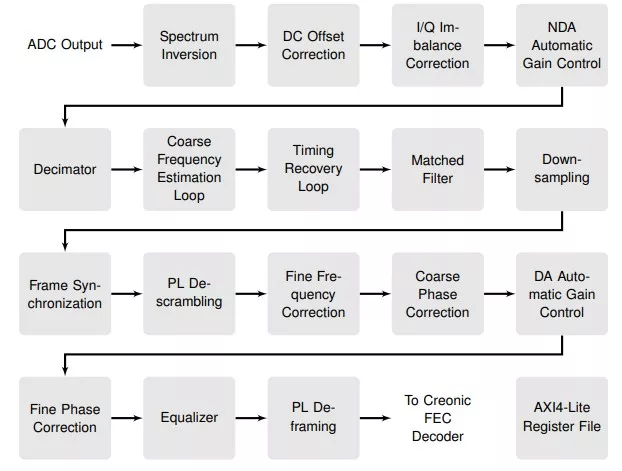

Block Diagram

Benefits

- Validated against 3rd party DVB-S2X modulators

- The demodulator contains radio interface, decimator, timing recovery, equalizer, frame acquisition, and carrier recovery

- Demodulator performs and supports spectrum inversion, DC offset correction, I/Q imbalance correction, decimation, coarse frequency estimation, timing recovery, matched filtering, downsampling, frame synchronization, PL descrambling, fine frequency correction, phase correction, automatic gain control, and PL deframing

-

- Low-power and low-complexity design.

- Very fast synchronization due to different sets of filter coefficients for acquisition and tracking mode

- Perfectly fits to the Creonic DVB-S2X LDPC/BCH decoder

- Available for ASIC and FPGAs (AMD Xilinx, Intel)

- Deliverable includes VHDL source code or synthesized netlist, VHDL testbench, and bit-accurate Matlab, C or C++ simulation model

Applications

- Satellite communication (Digital Video Broadcasting, Interactive Services, News Gathering, Professional Services)

- Nanosatellite and CubeSat devices

What’s Included?

- VHDL source code or synthesized netlist

- HDL simulation models

- Bit-accurate Matlab, C or C++ simulation model

- Comprehensive documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Modulation Demodulation IP core

Three Major Inflection Points for Sourcing Bluetooth Intellectual Property

Part 2: Opening the 5G Radio Interface

An Integrated, Tunable RF Filter: an Enabler for Reconfigurable Front-Ends

Design considerations for integrated CMOS receivers

Silicon IP for Programmable Baseband Processing

Frequently asked questions about Modulation and Demodulation IP cores

What is DVB-S2X Wideband Demodulator?

DVB-S2X Wideband Demodulator is a Modulation Demodulation IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Modulation Demodulation?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Modulation Demodulation IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.