10/100/1000 Ethernet MAC DO-254 IP Core

The 10/100/1000 Ethernet MAC Controller DO-254 IP Core implements the Media Access Control as specified in the IEEE 802.3-2008 sp…

Overview

The 10/100/1000 Ethernet MAC Controller DO-254 IP Core implements the Media Access Control as specified in the IEEE 802.3-2008 specification.

It can be configured to interface with the PHY through MII, RMII, GMII or SGMII, giving a wide choice to the user for the selection of the chip to connect to the physical layer. It can be configured to operate at 10 Mbps, 100 Mbps or 1000 Mbps, allowing the user to select the speed in base of their needs such as power, size, latency, etc.

The Ethernet MAC Controller has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit.

A radiation-hardened version with Triple Modular Redundancy (TMR) is also available.

Implementation Details

The figures below are indicative only, they may vary depending on the selected device, used tools, IP Core configuration and user added logic.

Unless otherwise specified all the runs have been performed with the default options of the respective tool. Register placement on the IO has been disabled.

Constraints were added for a GMII implementation or MII implementation. The results listed under the column “Maximum frequency of operation” are the worst case scenario (no multicycle, false paths, etc. defined).

The results are provided for an Ethernet MAC Core with ‘g_MDC_DIVIDER’ = 10, ‘g_MII_DATA_LENGTH’ = 8 for GMII, ‘g_MII_DATA_LENGTH’ = 4 for MII and without TMR (Triple Module Redundancy), if TMR is used the number of registers will be triplicated, the combinatorial logic will also increase and there might be a penalty on the maximum ‘clk’ frequency. The reported frequency is that needed for GMII (125 MHz), MII (25 MHz at 100 Mpbs).

Note: The results provided below are for some arbitrarily selected devices. If a device does not appear in a table below it does not mean that it is not supported. The Ethernet MAC Core can be implemented in any technology.

ACTEL/MICROSEMI

| FPGA Type | Maximum ‘clk‘ Frequency | Logic Modules (CORE) |

|---|---|---|

| ProASIC3

(A3P400 144FBGA I Std) |

50 MHz (MII; RMII) | 1947 |

| IGLOO

(AGL400V5 144FBGA I Std) |

50 MHz (MII; RMII) | 2019 |

| IGLOO2

(M2GL010T 484FBGA I Std) |

125 MHz (GMII) | SEQUENTIAL (R-cells): 583

COMB (C-cells): 995 |

| Fusion

(AFS600 484FBGA I -1) |

50 MHz (MII; RMII) | 2040 |

| Axcelerator

(RTAX250S 208CQFP Mil Std) |

50 MHz (MII; RMII) | SEQUENTIAL (R-cells): 685

COMB (C-cells): 1163 |

Note: The number of used logic modules is an approximation, since the tools do not provide detailed information of the resources used in a “per module” basis.

ALTERA

| FPGA Type | Maximum ‘clk’ Frequency | Flip-Flops | ALUTs | ALMs | Logic Cells |

|---|---|---|---|---|---|

| MAX II

(EPM2210FF324I5) |

50 MHz (MII; RMII) | 512 | – | – | 982 |

| Cyclone III

(EP3C5E144I7) |

125 MHz (GMII) | 514 | – | – | 1091 |

| Cyclone IV

(EP4CE22F17I7) |

125 MHz (GMII) | 513 | – | – | 1066 |

| Stratix II

(EP2S60F484I4) |

125 MHz (GMII) | 512 | 591 | 563 | – |

Note: MAX II compiled with MII options (‘g_MDC_DIVIDER’ = 10, ‘g_MII_DATA_LENGTH’ = 4)

XILINX

| FPGA Type | Maximum ‘clk‘ Frequency | Flip-Flops | 4-LUTs | Slices | Macrocells |

|---|---|---|---|---|---|

| CoolRunnerII

(XC2C128-6-TQ144) |

NA | NA | – | – | NA |

| Spartan3

(XC3S1000-5FG320) |

TX*: 100 MHz (MII) RX: 125 MHz (GMII) |

527 | 1007 | 677 | – |

| Spartan6

(XC6SLX45-3FGG484) |

125 MHz (GMII) | 527 | 619 | 271 | – |

| Virtex4

(XC4VLX15-12SF363) |

125 MHz (GMII) | 526 | 940 | 643 | – |

| Zync

(XC7Z010-3CLG400) |

125 MHz (GMII) | 516 | 502 | 303 | – |

Note *: The Transmitter needs further optimizations during synthesis and P&R.

Key features

- Configurable bit rate (1000 Mb/s, 100 Mb/s or 10 Mb/s)

- DAL A according to DO-254 / ED-80

- Compliant to the following clauses of the IEEE 802.3-2008 specification:

- §3. Media Access Control (MAC) frame and packet specifications

- §4. Media Access Control (full-duplex only)

- §22. Reconciliation Sublayer (RS) and Media Independent Interface (MII)

- §35. Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII)

- §36. Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) Sublayer, type 1000BASE-X (for SGMII option)

- §37. Auto-Negotiation function, type 1000BASE-X (for SGMII option)

- Compliant to the RMII specification (March 20, 1998)

- Compliant to the SGMII specification Revision 1.8 (optional)

- Fully synchronous design

- Simple interface to user’s logic

- TMR coding for radiation-hardening (optional)

- Technology independent (can be synthesized to any FPGA/ASIC vendor)

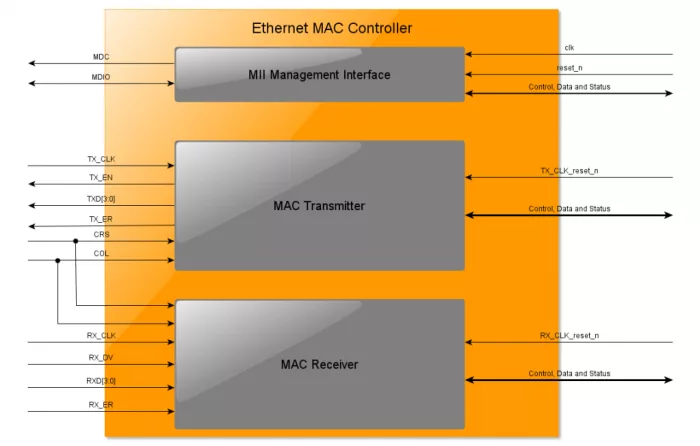

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 10/100/1000 Ethernet MAC DO-254 IP Core?

10/100/1000 Ethernet MAC DO-254 IP Core is a Ethernet IP core from SafeCore Devices listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.