Overview

DDR (Double Data Rate) SDRAM was introduced as a replacement for SDRAM memory running at bus speeds over 75MHz. DDR SDRAM is similar in function to the regular SDRAM but doubles the bandwidth of the memory by transferring data twice per cycle on both edges of the clock signal, implementing burst mode data transfer.

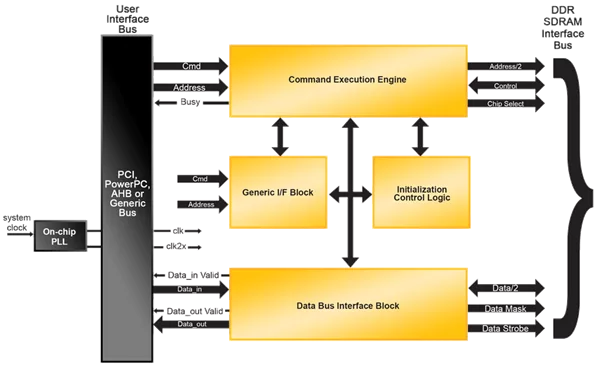

The DDR SDRAM Controller is a parameterized core giving user the flexibility for modifying the data widths, burst transfer rates, and CAS latency settings of the design. In addition, the DDR core supports intelligent bank management, which is done by maintaining a database of "all banks activated" and the "rows activated" in each bank. With this information, the DDR SDRAM Controller decides if an active or pre-charge command is needed. This effectively reduces the latency of read/write commands issued to the DDR SDRAM.

Learn more about DDR IP core

Brett Murdock, Dana Neustadter (Synopsys)

In recent years, emerging industries such as AI, Internet of Things, 5G, and intelligent networked vehicles have flourished, and the high requirements for performance have greatly increased the scale and complexity of chips, constantly challenging IP limitations.

Dana Neustadter, Senior Product Manager for Security Solutions, and Brett Murdock, Director, Product Line Management for Memory Interface IP, Synopsys Solutions Group

DDR is most critical IP to SoC’s successful operation, because processors in SoC typically spends the majority of its cycles on reading and writing to DDR memory.

This whitepaper provides an overview of the JEDEC memory standards to help SoC designers select the right memory solution, including IP, that best fits their application requirements.