DDR Memory Model

DDR Memory Model provides an smart way to verify the DDR component of a SOC or a ASIC.

Overview

DDR Memory Model provides an smart way to verify the DDR component of a SOC or a ASIC. The SmartDV's DDR memory model is fully compliant with standard DDR Specification and provides the following features. Better than Denali Memory Models.

DDR Memory Model is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

DDR Memory Model comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports DDR memory devices from all leading vendors.

- Supports 100% of DDR protocol standard JESD79F.

- Supports all the DDR commands as per the specs.

- Supports all device speeds as per specification.

- Supports Programmable CAS latency.

- Supports Programmable burst lengths: 2,4 and 8.

- Supports Write data Mask.

- Supports the following devices.

- X4

- X8

- X16

- Supports upto 1 GB device density.

- Supports the following burst types.

- Sequential

- Interleave

- Supports burst order.

- Supports for All Mode registers programming.

- Supports for Extended Mode registers programming.

- Supports Auto refresh & self refresh modes.

- Supports Auto precharge option for each burst access.

- Supports Power Down features.

- Supports input clock stop and frequency change.

- Supports DLL operation.

- Checks for following

- Check-points include power up, initialization and power off rules

- State based rules, Active Command rules

- Read/Write Command rules etc.,

- All timing violations

- Supports callbacks for user to get command data on bus.

- Quickly validates the implementation of the DDR standard JESD79F.

- Bus-accurate timing for min, max and typical values.

- Constantly monitors DDR behavior during simulation.

- Protocol checker fully compliant with DDR Specification JESD79F.

- Model, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

- Built in functional coverage analysis.

- Supports Callbacks, so that user can access the data observed by monitor.

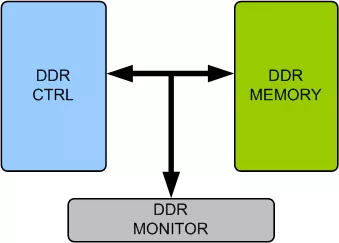

Block Diagram

Benefits

- Faster testbench development and more complete verification of DDR designs.

- Easy to use command interface simplifies monitor control and configuration.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the DDR testcases.

- Examples showing how to connect and usage of Model.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DDR IP core

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Secure DDR DRAM Against Rowhammer, RAMBleed, and Cold-Boot Attacks

DDR IP Hardening - Overview & Advance Tips

Which DDR SDRAM Memory to Use and When

DDR5/4/3/2: How Memory Density and Speed Increased with each Generation of DDR

Frequently asked questions about DDR Controller IP cores

What is DDR Memory Model?

DDR Memory Model is a DDR IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this DDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.