Overview

The DDR/DDR2 Synchronous Dynamic Random Access Memory (SDRAM) Controller MACO Core is a general-purpose memory controller that interfaces with industry standard DDR/DDR2 SDRAM devices and modules. This IP core is an IPexpress configurable core that provides the flexibility for modifying data widths, burst transfer rates, and CAS latency settings in a design. It provides a simple command interface for application logic. The controller can be configured to function as a DDR only or DDR2 memory controller.

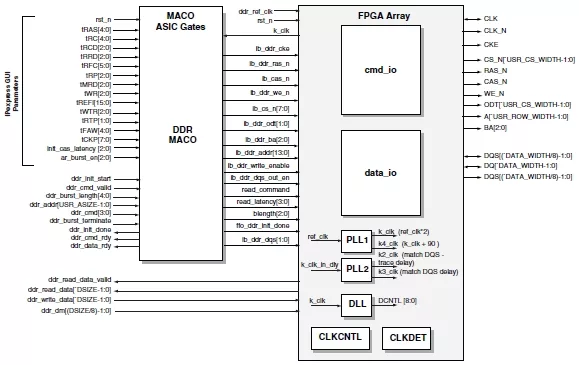

This proven DDR/DDR2 core is optimized utilizing MACO ASIC gates in the LatticeSCM devices, resulting in fast, small cores that utilize the latest architecture to its fullest.

Note the RLDRAM IP Core is implemented using both MACO ASIC gates and soft logic in the FPGA array. Since a significant portion of the implementation is in MACO, more of the FPGA Array is left for the user.

Software Requirements

* ispLEVER version 7.1 or later

* MACO design kit

* MACO license file

Learn more about DDR IP core

Brett Murdock, Dana Neustadter (Synopsys)

In recent years, emerging industries such as AI, Internet of Things, 5G, and intelligent networked vehicles have flourished, and the high requirements for performance have greatly increased the scale and complexity of chips, constantly challenging IP limitations.

Dana Neustadter, Senior Product Manager for Security Solutions, and Brett Murdock, Director, Product Line Management for Memory Interface IP, Synopsys Solutions Group

DDR is most critical IP to SoC’s successful operation, because processors in SoC typically spends the majority of its cycles on reading and writing to DDR memory.

This whitepaper provides an overview of the JEDEC memory standards to help SoC designers select the right memory solution, including IP, that best fits their application requirements.