CXL memory expansion

DenseMem increases effective CXL Type 3 Device memory capacity by a factor of 2x through transparent, in-line memory compression/…

Overview

DenseMem increases effective CXL Type 3 Device memory capacity by a factor of 2x through transparent, in-line memory compression/decompression with minimal impact to latency and badwidth. DenseMem is available as an area and power efficient drag and drop IP block portable across the latest process nodes.

Applications

Data Center operators at scale regularly employ software memory compression to create an additional memory tier to conserve capacity and interconnect bandwidth. Such operations consume monetizable host node compute cycles. DenseMem offloads compression/ decompression , tranparently creating a new, dynamically adjusting compressed memory tier within the Type 3 Device. DenseMem free up host cycles to service end user workloads. DenseMem supports industry standard compression algorithms for compatibility/ interoperability and alternatively offers propreitary compression algorithms for highest performance. DenseMem AI features adapt performance by adjusting to workloads automatically.

Integration

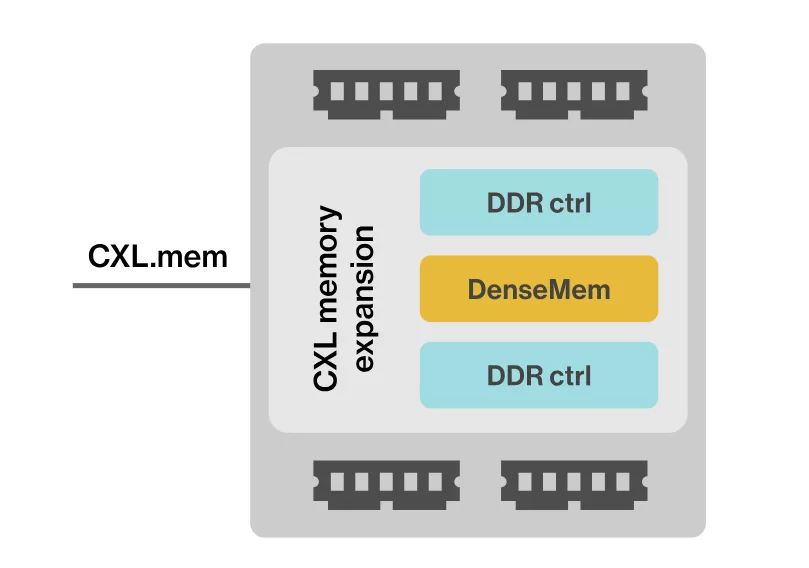

DenseMem can be integrated into the CXL Type 3 device SoC, between the CXL controller and memory controller logic blocks, supporting both AXI4 and CHI specifications. DenseMem lightweight firmware enables communication with the device over CXL.mem commands when reading and writing pages. DenseMem exposes compressed memory region as an additional Tier in the memory hierarchy, for easy integration into existing linux and software application stacks as well as CXL fabric management software.

Benefits

2-3x effective capacity increase. New compressed memory tier instantiated automatically inside CXL Type 3 device. Turn key solution: Real-time compression/decompression coupled with compaction, and transparent memory management. Operations at main memory speed and throughput. Compatible with AXI4/CHI specifications for easy integration. Intelligent real-time analysis and tuning to adapt to diverse workloads.

Performance / KPI

| Feature | Performance |

| Compression ratio: | 2-3x across diverse data sets |

| Frequency: | 1.6GHz (@5nm TSMC) |

| IP area: | Starting at 0.23mm2 (@5nm TSMC) 75% is SRAM |

| Memory technologies supported: | (LP)DDR4, (LP)DDR5 |

System integration of DenseMem

Integrated within a CXL Type 3 device

Key features

- Turn key solution: compression, compaction, memory management

- Automatic compressed memory tier

- Multi-instance support to match interface throughput

- Cache line granularity decompression for highest read performance (proprietary algorithm)

Block Diagram

Benefits

- Standards

- Protocol: CXL 2.0, 3.0, 3.1, cxl.mem

- Compression: LZ4, ZID (proprietary)

- AMBA interface: AXI4, CHI

- Architecture

- Transparent addressing to host

- Arbitrary cache line read/ write

- Bridge to cxl.mem, optionally to cxl.io

- Support for DCD, optional custom interface

- Type 3 device support, NUMA based memory tiering

What’s Included?

- FPGA evaluation license

- Encrypted IP delivery (Xilinx)

- HDL Source Licenses

- Synthesizable System Verilog RTL (encrypted)

- Implementation constraints

- UVM testbench (self-checking)

- Vectors for testbench and expected results

- User Documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is CXL memory expansion?

CXL memory expansion is a CXL IP core from ZeroPoint Technologies AB listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.