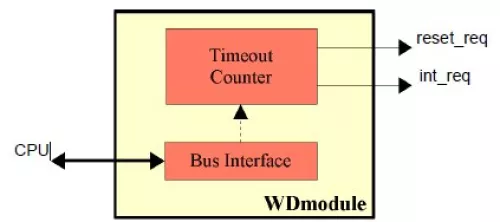

A watchdog is used in systems to prevent system lockup due to software or hardware failures. For normal operation, the timeout counter has to be reset by the CPU in a regular interval. Depending on the watchdog configuration, the watchdog asserts the reset_req and int_req outputs upon expiration of the timeout counters.

To avoid malfunction software to reconfigure the watchdog, all configuration registers are protected by a special lock key. The timeout interval can be configured over a wide range:

* min: 65536 system clock cycles

* max: 67'108'864 system clock cycles

Using a system clock of 40MHz, this results in a timeout window of 1.6ms – 1.67s.

Configurable Watchdog Timer (WD)

Overview

Key Features

- Two timeout outputs

- Configurable timeout interval

- Configuration register protected with lock key

- Timeout interval with 40Mhz clock:

- min: 1.6ms

- max: 1.67s

- Supports synchronous bus interfaces such as AMBA APB version 2.0

- Full synchronous design

- Synthesis Options:

- CPU readback enable

- Selectable lock key and reset key values

Benefits

- For gate-count optimization, the core can be configured to disable the configuration register read-back path. Synthesis options are included to use the core in 8, 16 and 32-bit systems. With a separate APB wrapper, the core can be used in ARM subsystems.

Block Diagram

Deliverables

- VHDL or Verilog RTL Source Code

- Functional Testbench

- Synthesys Script

- Data Sheet

- User Guide

- Hotline Support by means of phone, fax and e-mail

Technical Specifications

Foundry, Node

Technology independent

Maturity

Silicon proven in ASIC and FPGA Technologies

Availability

now