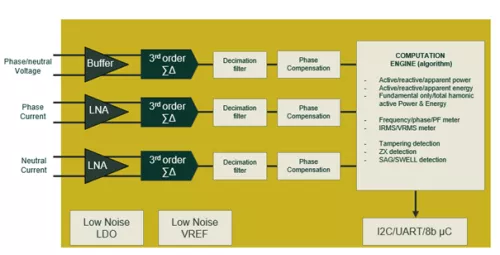

It is comprised of a high resolution Mixed-signal Front-End and of a dense Power and energy Computation Engine to achieve at the system-level a class accuracy as high as 0.1% (class accuracy of the product is 0.05%) over a range up to 1/10,000.

Complete measurement subsystem IP for single phase power metering

Overview

Key Features

- Embedded Computation Engine for utility biling applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

Block Diagram

Technical Specifications

Short description

Complete measurement subsystem IP for single phase power metering

Vendor

Vendor Name

Foundry, Node

Grace 130nm eFlash

Maturity

In Production

Related IPs

- Complete measurement analog front end (AFE) IP for single phase power metering in TSMC 40ULP

- Complete measurement analog front end (AFE) IP for three-phase power metering

- Complete measurement analog front end (AFE) IP for single phase power metering

- Complete measurement analog front end (AFE) IP for single phase power metering

- Complete measurement analog front end (AFE) IP for three-phase power metering

- Single Precision IEEE-754 complete FPU