Overview

CC-100IP-MB re-cycles system noise and surge current, preventing the deep discharge of system DC-Link and Reservoir Capacitors, reducing the amount of deep re-charge required from EV conversion system batteries. The IP creates inherent Capacitance Multiplication, Series Inductance Nullification, and Energy Harvesting functions that create the lowest Impedance point in the Conversion System Power Grids, enabling High frequency noise to be inserted into the CC-100IP-MB, aiding in maximum current recovery and Electric Vehicle Mileage extension, given a static battery size and capacity. The IP features a circuit noise activated dynamic input current controlled reservoir capacitance, and can function as a “stand-alone” system DC-Link or Reservoir Capacitor, or work in parallel with existing DC-Link Capacitor structures. Due to the embedded IP negative feedback, the CC-100 features a 25% reduction in capacitor effective series inductance (ESL). The IP operates by feeding back a portion (nominally 20%) of the bypass current flowing through the front end on chip input base capacitors, feeding back current into the Conversion System Power Grid, preventing bypass Capacitor Deep discharge, thus reducing overall chip dynamic power draw.

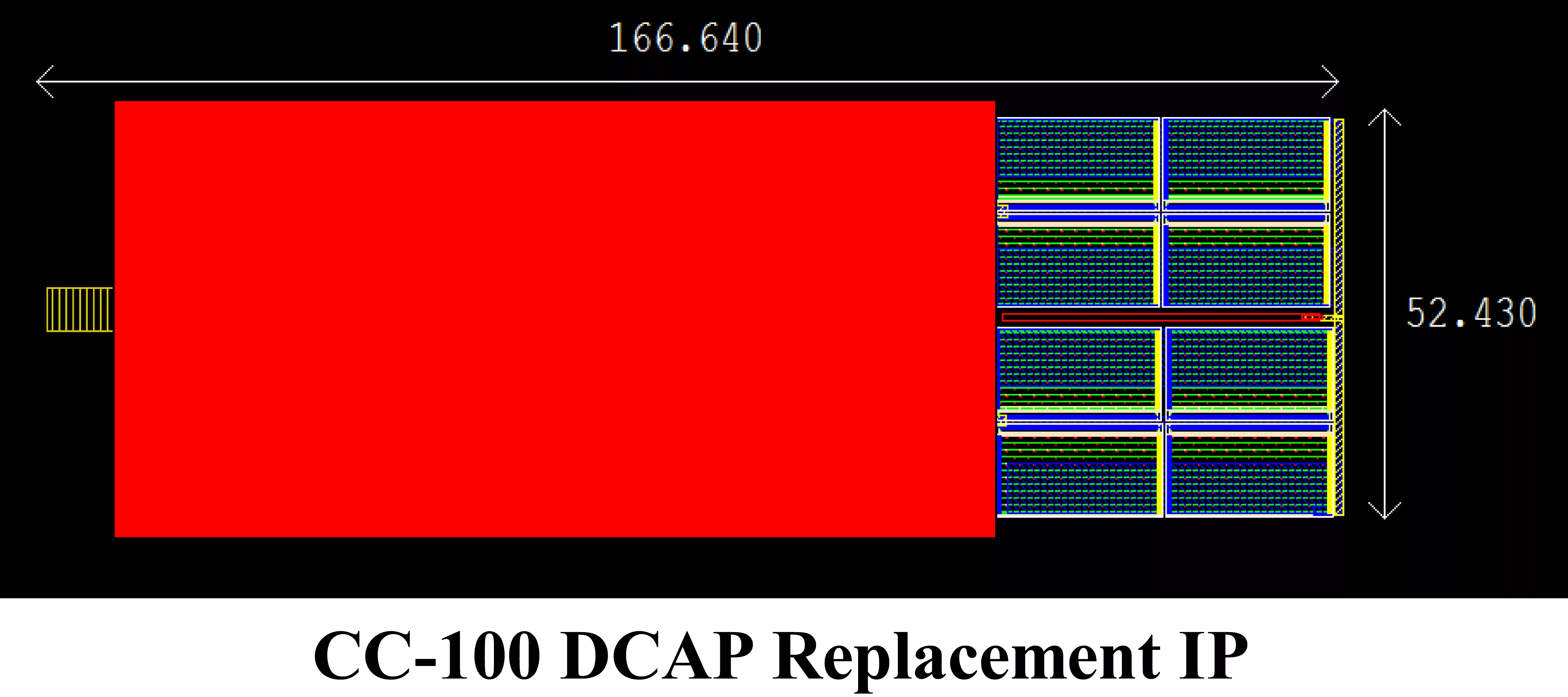

The Mileage Booster IP is meant to replace or work in parallel with existing DC-Link and Reservoir Capacitors, thus can be shaped into various aspect ratios and sizes to fit on-chip “white space”, the area under power grids, etc. in the same fashion as typical on-chip decoupling capacitors.

Learn more about Power Management Controller IP core

This article shows several ways to implement a power management controller using the new PMBus Revision 1.3 specification, and addresses several new considerations with architecting a system using this new specification.

Rivos is pleased to announce the successful secure provisioning of the integrated OpenTitan open source Root of Trust (RoT) in its SoC. This was done during the chip production process using the ZeroRISC provisioning appliance and platform.

Seven Steps to Create a Formal IP Specification

The USB 3.1 spec supports data rates up to 10 Gbits/second but poses new hurdles in link-layer design for chip designers, says an expert in the IP group at Synopsys.

The latest PCIe 6.x specification brings groundbreaking advancements in power efficiency and performance optimization. In this technical demonstration, Senior Principal Application Engineer Julien Eydoux showcases two features of Rambus’ PCIe 6.x Controller: L0p mode and FLIT mode operation.

This paper details first PCIe errors, error logging and then the error handling on a typical SoC.