FIFO based CAN Controller

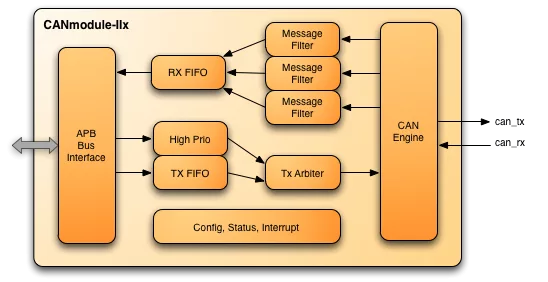

CANmodule-IIx is a full functional CAN controller module that contains message filtering, and receive-, and transmit buffers.

Overview

CANmodule-IIx is a full functional CAN controller module that contains advanced message filtering, and receive-, and transmit buffers. It is designed to provide a low gate-count CAN interface for FPGA and ASIC based system-on-chip (SOC) integrations.

Full message filtering together with a transmit FIFO and a high priority transmit message buffer support a wide range of applications. An AMBA Advanced Peripheral Bus (APB) interface enables smooth integration into ARM based SOC's.

Implementation Options

The core can be configured for your application to get a gate-count optimized implementation:

- Configurations readback enable

- Separate clock domains for CAN and system clock

- Fixed CAN configuration

- Selectable number of message filters: 0, 1, 2, or 3

- Data bus width: 8, 16, or 32-bit

Key features

- Standard Compliant

- Full CAN 2.0A/B compliant

- ISO 11898-1 compatible

- Supports standard CAN baud rates including 1 Mbps

- Receive Path

- 3 fully programmable message filters

- Each message filter covers: ID, IDE, RTR, data byte 1 and data byte 2

- 32 messages deep receive FIFO

- FIFO status indicator

- Message received time-stamp

- Transmit Path

- 16 messages deep transmit FIFO

- 1 message buffer for high priority messages to bypass transmit FIFO

- Message Arbiter

- System Bus Interface

- AMBA 2.0 Advanced Peripheral Bus Interface

- Other bus interfaces available upon request

- 8-bit, 16-bit, or 32-bit wide data path

- Status and configuration interface

- Programmable Interrupt Controller

- Local interrupt controller covering message and CAN error sources

- Target for FPGA Implementations

- Supports FPGA systems with two clock domains

- System clock (fast clock)

- CAN clock (slow clock, multiple of 8MHz)

- Test and Debug Support

- Listen only mode

- Internal loopback mode

- External loopback mode

- SRAM Based Message Buffers

- Optimized for low gate-count implementation

- 100% Synchronous Design

Block Diagram

Benefits

- Several special implementation options are available for gate count optimized implementations. These options have to be configured prior to synthesizing the design.

- Configuration register read-back enable

- To minimize gate count, the configuration register read-back path can be disabled

- Receive and transmit FIFO size can be adapted to system requirements

- Two separate clock domains

- A dedicated CAN clock is available when the system clock is too high for the CAN core. This feature can be disabled by a configuration entry.

- Fixed configuration

- For gate count optimized FPGA implementations, it might be desirable to set the configuration register to a fixed value.

- Message filter support

- 3 local message filters can individually be selected. This provides the option of having 0, 1, 2, or 3 CAN message filters available for the target application.

- Different Data Bus Interfaces

- Supports 32-bit APB, 16-bit, and 8-bit system bus interfaces

What’s Included?

- VHDL or Verilog RTL Source Code

- Verification Suite

- Functional Testbench including CANbus tranceiver model and additional CAN nodes

- Synthesys Script

- Data Sheet

- User Guide

- Hotline Support by means of phone, fax and e-mail

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is FIFO based CAN Controller?

FIFO based CAN Controller is a CAN / CAN-FD / CAN-XL IP core from Inicore, Inc. listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.