AXI Interconnect Fabric

The AXI Interconnect provides the necessary infrastructure to connect as many as 8 shared AXI Slaves to as many as 4 AXI Bus Mast…

Overview

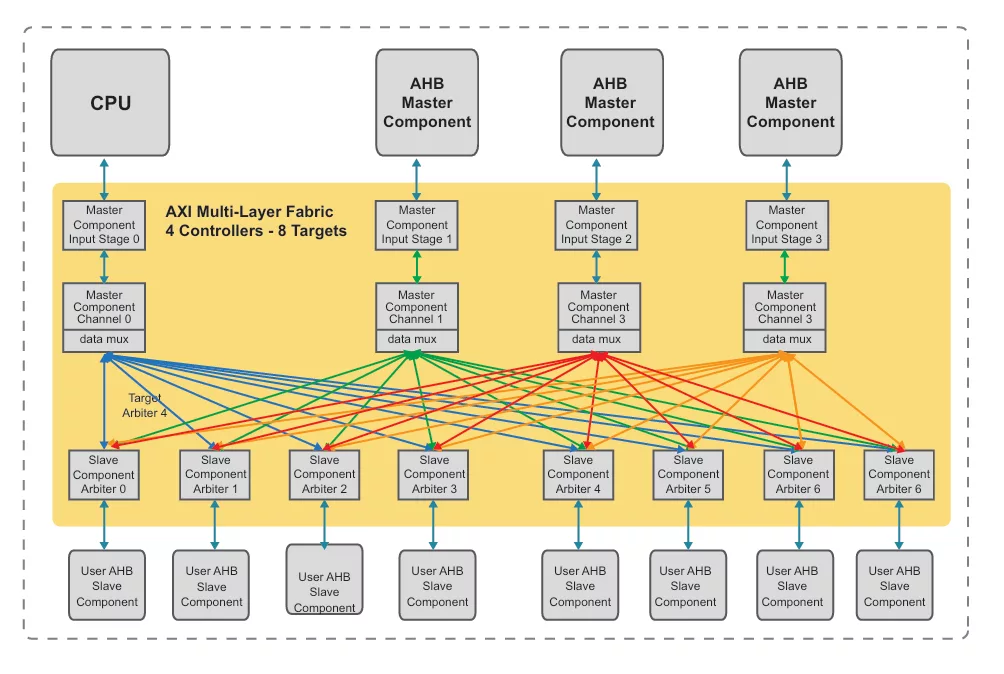

The AXI Interconnect provides the necessary infrastructure to connect as many as 8 shared AXI Slaves to as many as 4 AXI Bus Masters.

AXI defines 5 channels (write address, read address, write data, read data, write response) for its interface signaling between AXI Master and AXI Slave, but does not define a single way that an AXI Master must be connected to an AXI Slave. In general, an interconnect module is necessary when more than one Master and/or more than one Slave is required.

The AXI Interconnect is responsible for routing a transaction from a given Master to the appropriate Slave (decoding and switching), and ensuring that the various Master transactions do not interfere with each other

Key features

- AMBA® AXI-4 Compatible

- Multiple AXI Channels

- Off the shelf core supports 4 Masters and 8 Slaves

- Arbitration is done at each slave

- Other configurations are available

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- AXI Bus Functional Model

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is AXI Interconnect Fabric?

AXI Interconnect Fabric is a Network-On-Chip IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.