The FFT/IFFT/DCT engine is an application specific instruction set processor (ASIP) optimized for the implementation of Fourier and cosine transforms, while also supporting general FIR equations.

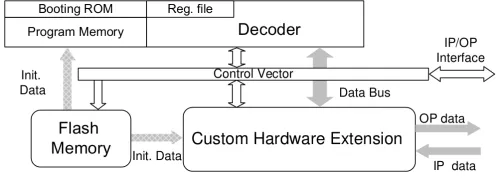

The engine is divided into two main parts: a processing element, which deals directly with the data, and an embedded processor to control the signal flow by configuring the processing element. The system architecture is shown in the Fig.

ASIP-2

Overview

Key Features

- Platform to design Application Specific Instruction Set Processors (ASIPs).

- Ideal for supporting multi-standard systems.

- Supports a wide range of complex DSP functions.

- The ASIP2 performs Fast Fourier Transform (FFT) to convert time domain signals to frequency domain signals for further processing. It supports FFT sizes from 4 to 8K.

- The ASIP2 is a super set of ASIP1 (VK-701) developed by Wasiela

- Ported C compiler, assembler, linker, and debugger suitable for the two sample targets.

- The ASIP2 targets pack up to six independent operations to be executed in parallel in one instruction word of 32~bits.

- Ability to easily target other signal processing applications.

Benefits

- Flexible

- Performance approaches that of dedicated implementations.

- Software-like ease.

Block Diagram

Applications

- Wired/Wireless MODEMs (DSL, LTE, Zigbee, ...)

- Image processing

- Speech recognition/Speech synthesis

- Filters, decimators, and interpolators

Deliverables

- Synthesizable Verilog

- Software Tools

- – Engine compiler for easy programming process.

- – Generator for flash memory initialization file.

- – Optimum scale factor pattern calculator for:

- * Max SQNR

- ∗ Certain RMS

- – Microcode Assembler

- System Model (Matlab code) and documentation

- SystemVerilog Test Benches

- Documentation

Technical Specifications

Maturity

Mature

Availability

Now