Overview

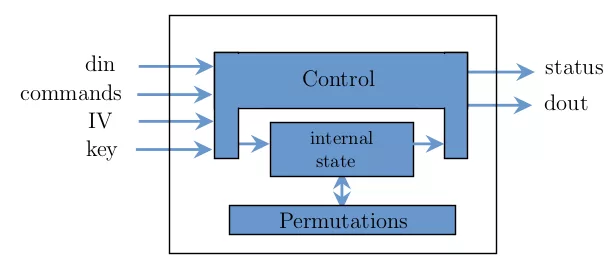

XIP2201B from Xiphera is an Intellectual Property (IP) core for Ascon authenticated encryption with associated data (AEAD) and hashing.

It supports three variants of AEAD as well as two variants of hashing and extendable output functions (XOF). Notably, XIP2201B provides three different cryptographic primitives all in one IP core. Ascon was selected by the National Institute of Standards and Technology (NIST) to be standardized as the lightweight cryptographic algorithm.

XIP2201B for authenticated encryption and decryption, hashing, and extendable output function operation for all Ascon variants defined in the standard.

Ascon was selected as the lightweight cryptographic algorithm by NIST and can thus be expected to see usage in the coming years. The algorithm itself is optimised to be small in size, support many features, and be especially efficient with small inputs.

The XIP2201B is optimised for both moderate resource usage and fast computation.

Learn more about Symmetric Crypto IP core

The cybersecurity threat landscape is dynamic and rapidly evolving. Indeed, attackers are constantly finding new ways to exploit critical vulnerabilities across a wide range of applications and devices. Protecting data and devices requires secure processes running on systems and networks.

The goal of this white paper is to provide a primer introduction to RoT and how to choose a right RoT as the trust anchor for a novel hardware based security architecture

A Root of Trust is the foundation on which all secure operations of a computing system depend. It contains the keys used for cryptographic functions and enables a system-wide secure boot process. It is inherently trusted and therefore must be secure by design.

Encryption requirements are now found in almost every new SoC design. This paper focuses on symmetric offload in a packet processing system for IPsec but the concepts apply equally well to SSL, SRTP and link security.