Vendor:

iWave Systems Technologies Pvt. Ltd.

Category:

Video Transport

ARINC 818-2 IP Core

iWave's ARINC IP core is ARINC 818–compliant, which can be implemented on any transceiver based FPGA.

Overview

iWave's ARINC IP core is ARINC 818–compliant, which can be implemented on any transceiver based FPGA. It can be used for both transmit-and-receive applications. This core has flexible user interface, allowing for various video parameter configuration. This IP core supports Line Synchronous Mode.

Key features

- Streaming Interface used as Video TX and RX interface.

- Video Input Format Supported.

- Resolution depends on the FPGA transceiver speed used for implementation

- For SXGA (1280x1024@60Hz) resolution, required data rate is 2.5Gbps

- Pixel Format supported.

- Monochrome

- RGB

- YcbCr

- RGBA

- Pixel Aspect ratio supported.

- 1:1

- 1:1.2

- 1.2:1

- NTSC (approx 8:9)

- PAL (16:15)

- Frame Rate supported.

- 15fps

- 20fps

- 24

- 24 * 1000 / 1001

- 25 (PAL)

- 30

- 30 * 1000 / 1001 (29.97 NTSC)

- 60

- 50

- 60 * 1000 / 1001 (59.94 NTSC)

- 50 (VESA DMT)

- 60 (VESA DMT)

- 75 (VESA DMT)

- 85 (VESA DMT)

- 50 (VESA CVT)

- 60 (VESA CVT)

- 75 (VESA CVT)

- 85 (VESA CVT)

- Pixel Table Number supported

- 8-bit Components, four components per transmission word

- Pixel Array Order supported

- Left to Right, Top to Bottom

- Line Synchronous Mode supported

- 32-bit Full Image CRC supported

- Following are user configurable parameters

- No. Of rows

- No.of Columns

- Video Format Code

- Pixel Aspect Ratioe

- Video Frame rate

- Color Information Code

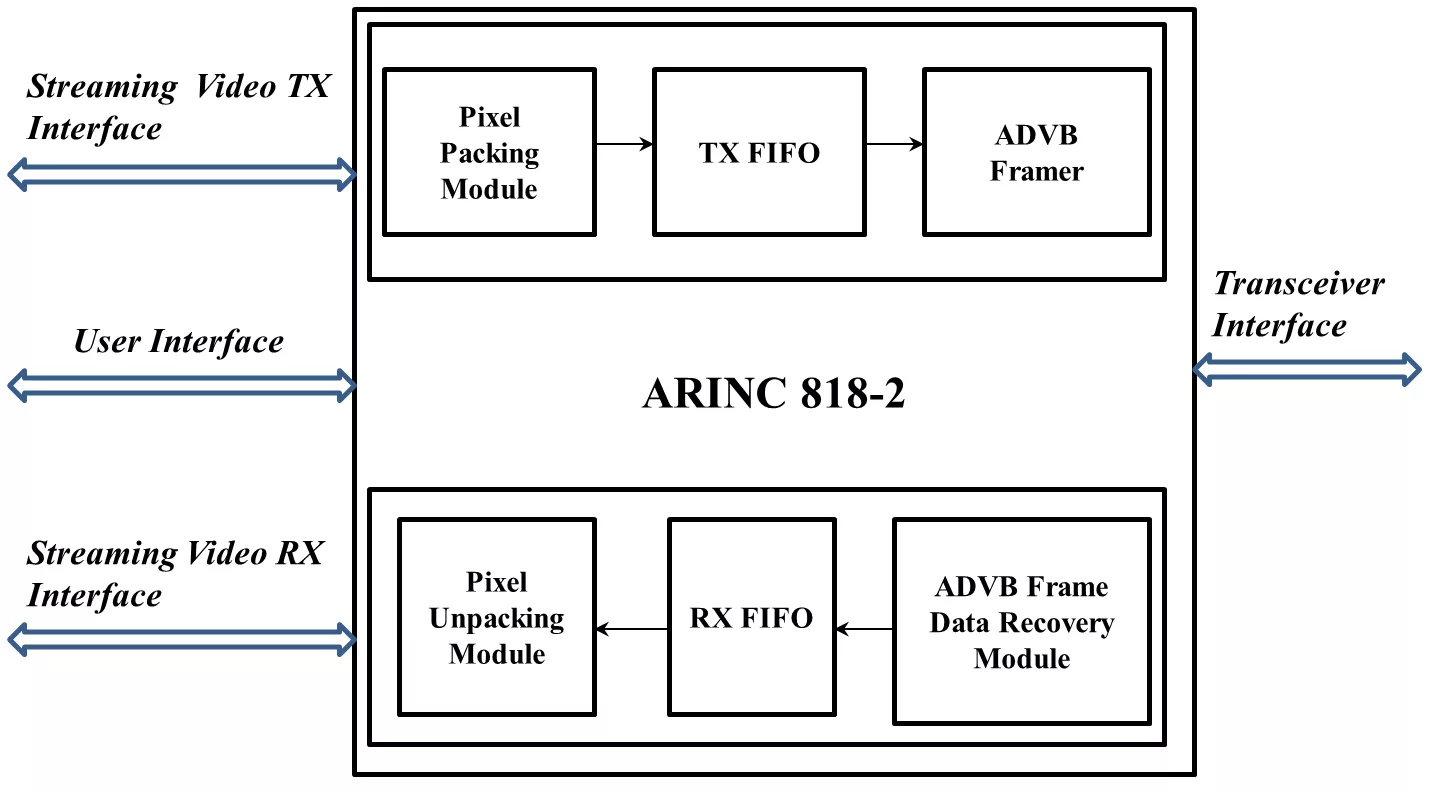

Block Diagram

ARINC 818-2 IP Core block diagram

Benefits

- Design consists streaming interface and hence it can be used for high throughput video transfer.

Applications

- Video and image processing in Aerospace applications.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Part Number

ARINC 818-2 IP Core

Vendor

iWave Systems Technologies Pvt. Ltd.

Provider

iWave Systems Technologies Pvt. Ltd.

HQ:

India

iWave Systems is a technology oriented organization founded in 1999 by enterprising technocrats, each with two decades of experience in the areas of Hardware and Embedded Software. We are an International design house with an energetic team of professionals with extensive experience in engineering real time embedded Systems.

iWave Systems is poised to empower today's technology demands with appropriate, custom designed embedded system solutions. Our focus is in providing effective and efficient solutions to our customers at an optimal cost with an accelerated time-to-market. We help our customers worldwide to explore and leverage the state of the art technologies and achieve excellence in their business objectives.

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Tfox

Enabling High Performance SoCs Through Multi-Die Re-use

This paper gives a high-level overview of a technique for rapid design of new IC designs using multiple dice packaged in a variety of aggregations allowing for differnent performance levels and price points to be achieved. The technique relies on a new high-bandwidth low pin-count communication channel between two or more dice.

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

This paper presents the interconnect solution adopted for an HDTV SoC developed in HVD division of STM. The SoC is a one-chip satellite HDTV set-top box IC developed in 65nm technology. The interconnect of this HDTV SoC is the first in STM implementing a mixed architecture based on the circuit-switched interconnect named STBus and the new NoC interconnect named VSTNoC.

Steps for Delivering Multimedia Over 5 GHz WLANs

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

The H.264 Scalable Video Codec (SVC) reduces network bandwidth, eliminates transcoding, and simplifies storage management. Here's how it works.

Frequently asked questions about Video Transport IP cores

What is ARINC 818-2 IP Core?

ARINC 818-2 IP Core is a Video Transport IP core from iWave Systems Technologies Pvt. Ltd. listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.