The ARC-V™ RPX-100 series processors feature a dual-issue, 64-bit superscalar architecture for use in high performance applications where performance efficiency is required. The cores offer outstanding performance delivering minimal power consumption.

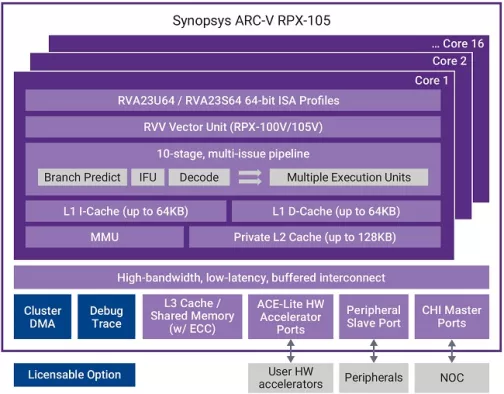

The ARC-V RPX-100 processors are based on the RISC-V instruction set architecture (ISA). The processors feature a physical address space defined by the RISC-V Sv39 MMU. For applications requiring higher performance, the multi-core RPX-105 & RPX-105V are available with up to 16 CPU cores and up to 16 hardware accelerators in the processor cluster. RISC-V vector extensions (RVV) are available in the RPX-100V (single core) and RPX-105V (multi-core) processors.

The ARC-V RPX-100 features level 1 (L1) instruction and data cache optimized for use in performance efficient applications. Each core also supports up to 128KB of private L2 cache. The multi-core cluster supports an additional 16MB of cluster shared cache (L3).