The ARC® HS44, HS46, and HS48 processors feature a dual-issue, 32-bit superscalar architecture for use in embedded applications where high-performance and high clock speed are required. The cores can be clocked at up to 1.9 GHz in 16ff processes (worst case, single core, base configuration) and offer outstanding performance delivering 3.0 DMIPS/MHz and 5.2 CoreMark/MHz with a small area footprint and low power consumption.

The ARC HS44, HS46 and HS48 processors are based on the advanced ARCv2 instruction set architecture (ISA) and pipeline, which provides leadership power efficiency and code density. For applications requiring higher performance, dual- and quad-core versions of all three ARC HS4x processors are available.

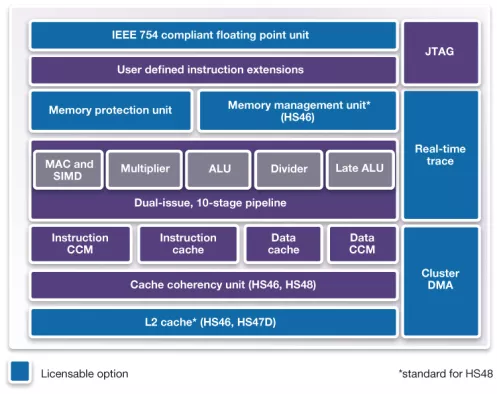

The ARC HS44 features close coupled memory (CCM) and is optimized for use in applications where real-time, deterministic behavior is required. The HS46 is designed for high-performance embedded applications that require cache and includes all of the features of the HS44 plus support for up to 64K Level 1 (L1) instruction and data cache. The HS48 is designed for use in applications running Linux or SMP Linux. The HS48 has all of the features of the HS46 plus support for up to 8MB of L2 cache, as well as a Memory Management Unit (MMU) supporting a 40-bit physical address space and page sizes up to 16 megabytes (MBs).

The HS44, HS46 and HS48 are designed to be used in applications such as SSD controllers, home networking, automotive systems, smart appliances, and many other high-end embedded applications.