APB Interrupt Controller

The interrupt controller monitors interrupts from all other modules within the system and issues interrupt requests to the proces…

Overview

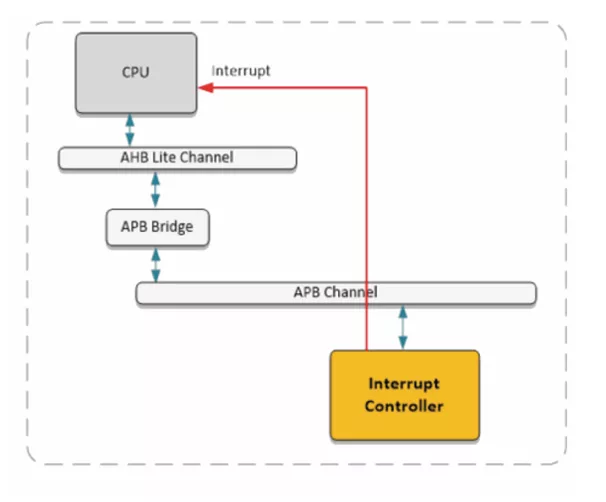

The interrupt controller monitors interrupts from all other modules within the system and issues interrupt requests to the processor when necessary. The interrupt controller is scalable to support from 1 to 32 interrupt sources. It also provides enable set and enable clear mechanisms to prevent dangerous read-modify-write operations. It provides active high & active low IRQ & FIQ interrupt request outputs.

Key features

- AMBA® APB Compatible

- Up to 32 independent interrupt sources

- FIQ and IRQ outputs

- Single bit enable and clear control

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- APB Bus Functional Model

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Interrupt Controller IP core

Easy migration from Arm to RISC-V: an L110 case study

Migrating the CPU IP Development from MIPS to RISC-V Instruction Set Architecture

A formal-based approach for efficient RISC-V processor verification

A closer look at Arm A-profile support for non-maskable interrupts

SOC Stability in a Small Package

Frequently asked questions about interrupt controller IP cores

What is APB Interrupt Controller?

APB Interrupt Controller is a Interrupt Controller IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this Interrupt Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Interrupt Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.