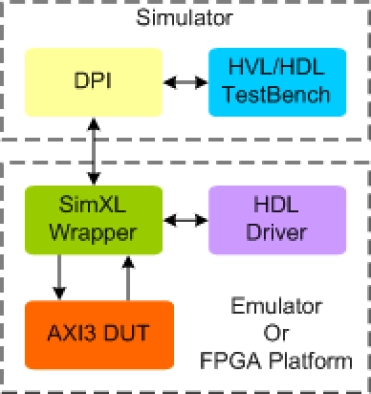

AMBA AXI3 Synthesizable Transactor provides a smart way to verify the ARM AMBA AXI3 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's AMBA AXI3 Synthesizable Transactor is fully compliant with standard AMBA AXI3 Specification and provides the following features

AMBA AXI3 Synthesizable Transactor

Overview

Key Features

- Compliant with the latest ARM AMBA AXI3 Protocol Specification.

- Supports AXI3 Master and Slave.

- Supports all AXI3 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths, burst sizes and response types.

- Supports constrained randomization of protocol attributes.

- Separate address, data and response phases. Separate read and write channels.

- Support for burst-based transactions with only start address issued.

- Slave supports fine grain control of response per address or per transaction.

- Programmable wait states or delay insertion on different channels.

- Ability to inject errors during data transfer.

- Write strobe support to enable sparse data transfer on the write data bus.

- Narrow transfer support.

- Unaligned address access support.

- Ability to issue multiple outstanding transactions.

- Out of order transaction completion support.

- Protected accesses with normal/privileged, secure/non-secure and data/instruction

- Support for Write data phase before Write address phase.

- Ability to configure the width of all signals.

- Support for bus inactivity detection and timeout (configuration parameter and dynamic change of inactivity timer).

- Write data and read data interleaving support.

- Configurable write and read interleave depth.

- Programmable interleave size per transaction to allow fixed and variable data interleaving in a transaction.

- Atomic access support with normal access, exclusive access and locked access

- Programmable Timeout insertion.

- Rich set of configuration parameters to control AXI3 functionality.

- On-the-fly protocol and data checking.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Callbacks in master and slave for various events.

- Status counters for various events on bus.

Benefits

- Compatible with testbench writing using SmartDV VIP's

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the AMBA AXI3 Synthesizable testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

AMBA AXI3 Synthesizable Transactor

Vendor

Vendor Name