8-Bit Microcontroller Based on the W65C02

The W65C02i1M08SC Microprocessor Datasheet is for MyMENSCH™ Rev-A.

Overview

The W65C02i1M08SC Microprocessor Datasheet is for MyMENSCH™ Rev-A.

The central processor unit (CPU) is the W65C02RTL microprocessor. The W65C02i1M08SC is described with the Verilog

HDL for use with MAX10 FPGAs.

WDC's RTL Softcore version provides a cycle-accurate option providing for implementation onto any foundry process.

Development tools are available for the creation of 65xx application code.

Key features

- -8-bit data bus

- -Intel PSG MAX10M08SC FPGA with 8,000 Logic Elements Available

- -Operating Voltage – 3.3V

- -W65C02RTL MPU @ 14.7456 MHz with external memory bus for memory and module expansion

- -W65C22RTL VIA (x2)

- -W65C51RTL ACIA (x3) – ACIA XTLI Operation Speed – 1.8432 MHz

- -W65CGPIO 5 register and 2 register

- -De-bounced Keypad GPIO_A

- -W65CHBM Hardware Breakpoint Module

- -SPI Master

- -I2C Master

- -WDC 2K byte for 2048 bytes of CFM MyMENSCH™ Monitor for boot loading and debugging code

- -30K bytes for a total of 30,720 bytes for User code SRAM boot loaded from USB or copied from UFM

- -12K bytes for a total of 12,288 bytes for data SRAM

- -JTAG available on MyMENSCH™ Rev-A on J4

- -16×16 Hardware multiplier (x2 – Signed and Unsigned)

- -32K bytes for a total of 32,768 bytes of User FLASH Memory (UFM)

- -64-bit Unique Chip ID/serial number programmed in the Intel MAX10 factory

- -18,446,744,073,709,551,616 Unique IDs

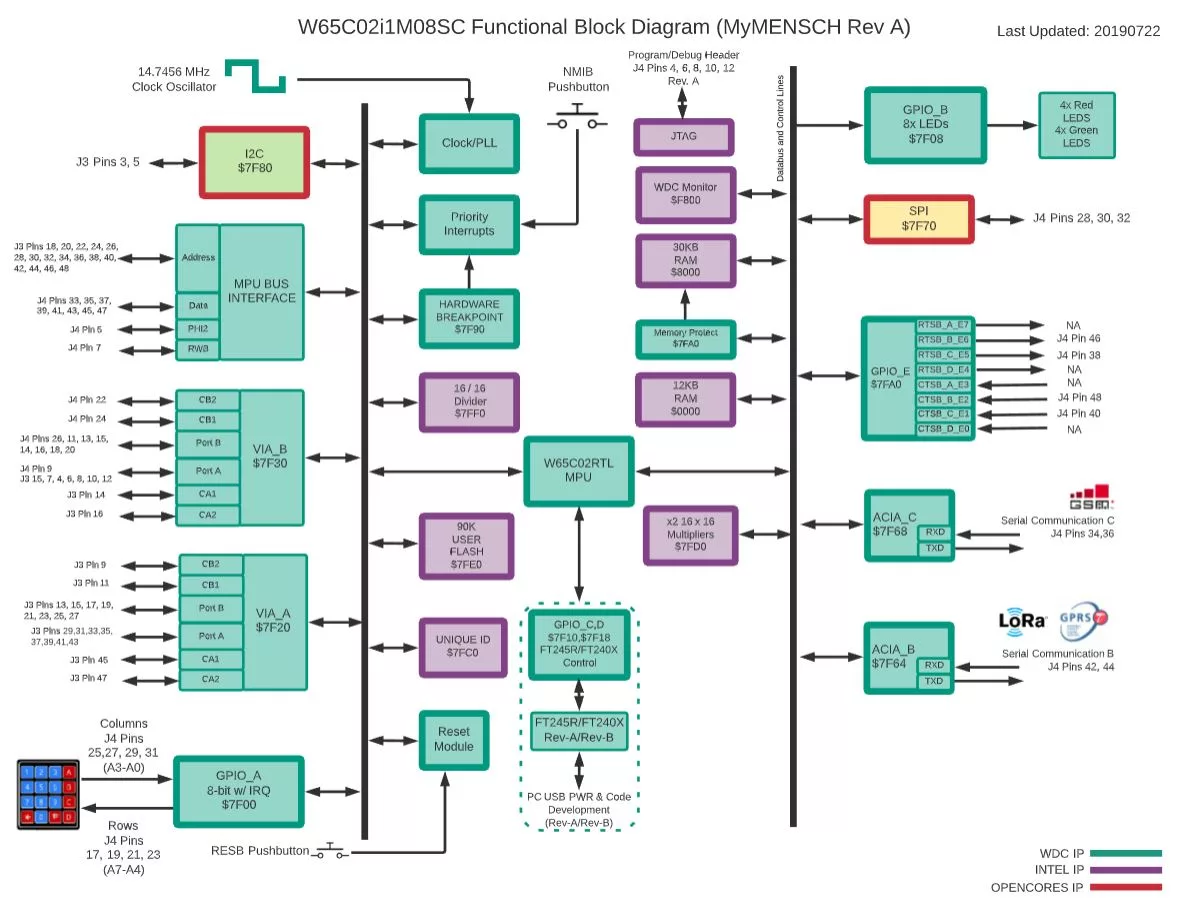

Block Diagram

Benefits

- #NAME?

Applications

- IoT

- Industrial Controls

- General Electronics

What’s Included?

- Preprogrammed FPGA Devices

- Code Examples

- Datasheet Documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about MCU IP core

Why Did Ambiq Micro Select HiFi-5 DSP IP for Next Generation MCU?

Upgrading 8- and 16-bit MCU designs: Development ecosystem

Adding DSP hardware shrinks energy for MCU core

Advanced BLDC Motor Control using Freescale Ultra Reliable MPC5676R/MPC5674F MCU

Cortex-M7: 6-stage, cached, 400 MHz MCU

Frequently asked questions about MCU IP cores

What is 8-Bit Microcontroller Based on the W65C02?

8-Bit Microcontroller Based on the W65C02 is a MCU IP core from Western Design Center, Inc. listed on Semi IP Hub.

How should engineers evaluate this MCU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MCU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.