64-bit High performance Single Core Microprocessor

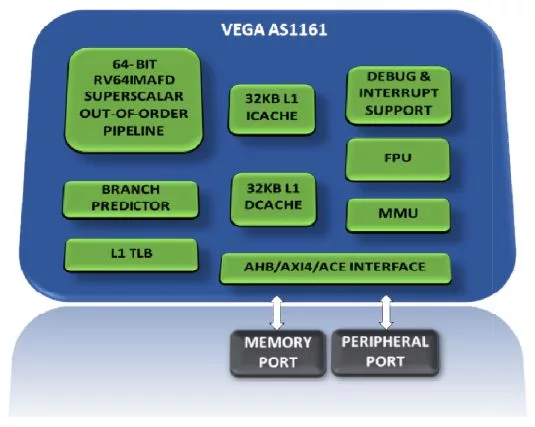

VEGA AS1161 features an out-of-order processing engine with a 16 stage pipeline enabling it to meet next gen computational requir…

Overview

VEGA AS1161 features an out-of-order processing engine with a 16 stage pipeline enabling it to meet next gen computational requirements. The processor also supports single and double precision floating point instructions, and MMU for Linux based applications. AS1161 is optimized for high performance with integrated Instruction Cache, Data Cache and an advanced branch predictor enabling efficient branch execution. Features also include PLIC and vectored interrupts for serving various types of system events. An AXI or AHB interface enables ease of system integration and JTAG debug interface for development support.

Key features

- RISC-V 64G (RV64IMAFD) ISA

- 13-16 stage out-of-order pipeline implementation

- Advanced branch predictor: BTB, BHT, RAS

- Harvard architecture

- Privilege Levels : User-, Supervisor- and Machine-mode

- Fully-featured memory subsystem with Linux support

- Memory Management Unit

- Page-based virtual memory

- Configurable L1 caches

- High-performance IEEE 754-2008 compliant floating-point unit

- Vectored interrupt support

- Platform Level Interrupt Controller

- Up to 127 IRQs

- Low interrupt latency

- AXI4- / ACE, AHB- compliant external interface

- Advanced Integrated Debug Controller

- JTAG compliant interface

- HW/SW breakpoints support

- Debug extension allowing Eclipse debugging via a GDB

- openOCD

- JTAG connection

- Linux compatible

- Zephyr compatible

- FreeRTOS port

Block Diagram

Applications

- Media Server

- Single Board Computer

- Storage devices

- Energy Gateway

- Electricity Grid and Distribution

- Building Safety

- Circuit Breaker

- Smart Power Socket, Light Switch

- Networking

- Medical Imaging

- Defibrillator

- Hospital Admission Machine

- Powered Patient Beds

- Vital Signs Monitor

- Biometric access control

- Public Address Systems

What’s Included?

- RTL Source Code

- Test Benches

- Synthesis Scripts

- Product Specification

- User Guide

- Integration Guidelines

Video

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 64-bit High performance Single Core Microprocessor?

64-bit High performance Single Core Microprocessor is a CPU IP core from C-DAC listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.