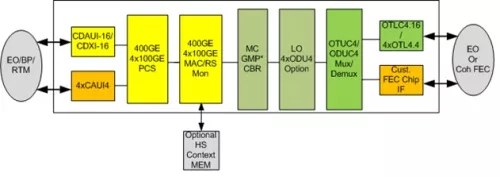

Alphawave offers a dynamically reconfigurable OTUC4 and 2xOTUC2 OTN (Callite-C4) digital wrapper IP core solution. The IP core is a perfect choice for carrying 400GE (IEEE 802.3bs) signal, 100GE signal or future 200GE signal over Optical Transport Network. Software can configure the IP core into 1xOTUC4 mode, 2xOTUC2 mode and 4xOTU4 mode dynamically.

The Core supports 3 levels of OH insertions and extractions : register programming, memory programming and external programming via a dedicated OH port. It comes with Optional GFEC core, which can be bypassed when connected with external high-gain FEC or Coherence module. The OTN core supports full alarm and OH inserts and extracts as specified in ITU G.709 and ITU G.798.

400G : OTUC4 / 2xOTUC2 / 4xOTU4 Digital Wrapper

Overview

Key Features

- Line Interface

- OTUC4

- OTUC2

- OTU4

- with or without G.709 GFEC

- OE interface : OTL4.x

- Proprietary External FEC / Coherence Interface

- Client Interface

- GMP

- LO ODU

- OTN Mapper +GFEC

- Maps GMP mapped to OPU4

- OTU4/ODU4/OPU4 or OTUC4/ODUC4/OPUC4 Overhead generation including alarms. OH fields programmed through software registers or via an OH insertion interface.

- 709 GFEC generation

- Optional using external proprietary FEC encoding

- OTN De-mapper +GFEC

- ODUC4/OTUC4, ODUC2/OTUC2 or ODU4/OTU4 frame alignment with programmable FAS

- ODUC4/OTUC4, ODUC2/OTUC2 or ODU4/OTU4 overhead processing including detection of faults

- OTUC4/ODUC4/OPUC4, , ODUC2/OTUC2/OPUC2 or OTU4/ODU4/OPU4 overhead monitoring. Capture of registers for software processing of slow changing fields or option to send to an OH extraction interface for processing by an external device.

- 709 GFEC decode processing

- Optional using external proprietary FEC decoding

- Processor Interface

- Simple request-acknowledge register access to 32-bit registers for device configuration and statistic collection.

- Optional AXI4-lite interface

- Application Programming Interface

- Complete API for ease of use for configuration, error processing and monitoring.

Benefits

- Cost effective – Low cost replacement for multiple ASICs solution

- Power efficiency – Low power replacement for multiple ASICs solution

- Higher port density per card – space efficiency

- Timing transparency on each lane.

Block Diagram