Overview

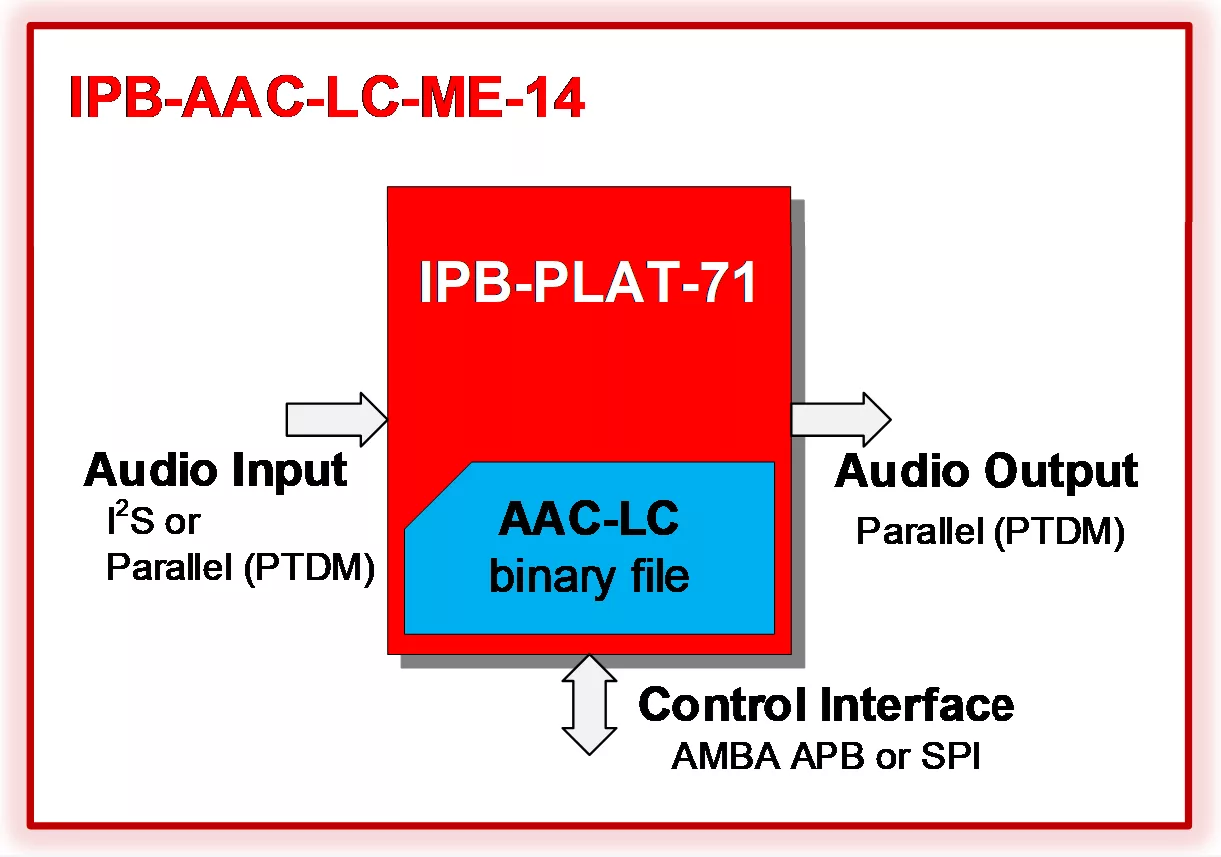

The IPB-AAC-LC-ME-14 is an IP core for encoding up to 14 stereo audio streams in real-time, in one of the following configurations: 14 stereo channels or 12 stereo channels and a 5.1 channel.

The IPB-AAC-LC-ME-14 software requires an audio engine platform named IPB-PLAT-71, which includes 7 processors and one accelerator.

The encoder can be configured, run and monitored by means of a configuration, control, and status register file accessed by APB or SPI.

Learn more about Audio Analog IP core

In the massive world of multimedia, sound stands as a vital component that adds depth to the overall encounter. Whether it's streaming services, video games, or virtual reality, sound holds a crucial role in crafting immersive and captivating content.

Design and evaluation of power-efficient SoCs

By integrating an audio analog codec that implements the 'audio hub' functionality and is able to process and mix audio signals from asynchronous sources, system designers can free the scarce main processor resources for more relevant tasks and simplify the system design, thus achieving a more effective solution.

Consumer IC Advances -> Altering algorithms to create '3D' sound

Efficient audio is essential for low-power 3G mobiles

The virtual validation of subsystem performances (Pop-up Noise, Signal-to-Noise Ratio, Power supply Noise, Power consumption...) requires the modeling and simulation of complete subsystems. Application Hardware Modeling (AHM) consists in addressing the risks of performance degradation while integrating a Silicon IP in its Integrated Circuit (IC) and this IC on its Printed Circuit Board (PCB). The selection of relevant models for a subsystem performance, along with the creation and validation of models through equivalence checking, are the basics of Application Hardware Modeling for right-on-first-pass subsystems!