Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

By Brandon LoGuercio, Trilinear Technologies

As video resolutions, refresh rates, and color depths push bandwidth demands to new extremes, system designers face increasing challenges in maintaining signal integrity over longer cable lengths and complex routing environments. DisplayPort 2.1 addresses these issues with features like UHBR (Ultra High Bit Rate) signaling and robust link training. But when standard signal traces aren’t enough, LTTPR Link Training Tunable PHY Repeater steps in as a vital enabler.

At Trilinear Technologies, we design DisplayPort IP that’s built not just for compliance, but for practical integration into demanding applications. LTTPR support is quickly becoming a cornerstone of next-gen DisplayPort architectures, particularly in automotive, industrial, and multi-display environments. Here's what you need to know.

What is LTTPR?

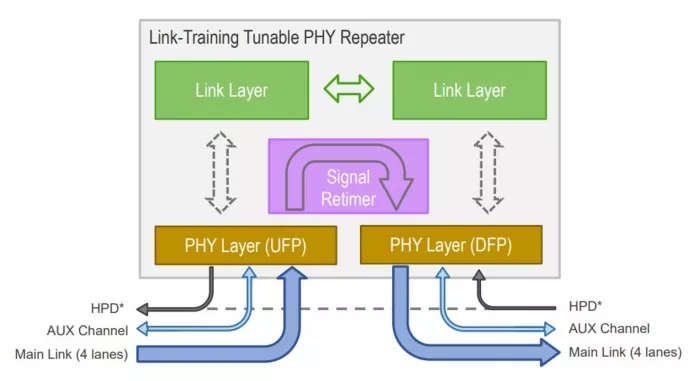

LTTPR stands for Link Training Tunable PHY Repeater, a repeater architecture defined in the DisplayPort 2.1 standard. It allows high-speed DisplayPort signals to traverse extended or complex interconnects while maintaining transparent link training. Unlike legacy redrivers or simple retimers, LTTPRs actively participate in the training process across each segment between source and sink.

Each LTTPR can adaptively retime and equalize signals, preserving signal quality even at UHBR20 (20 Gbps/lane) speeds. It also forwards the AUX channel — essential for link training, EDID reads, HDCP authentication, and MST negotiation — without introducing disruptive latency or breaking protocol continuity.

Why LTTPR is Critical in Modern Display Systems

With UHBR link rates becoming the norm, physical limitations of copper interconnects pose significant challenges:

- Increased insertion loss and crosstalk

- Layout restrictions for PCB routing

- Costly materials required to extend signal range

LTTPRs mitigate these issues by dividing the link into multiple training domains, effectively boosting signal integrity and layout flexibility. In long-reach applications, such as automotive and extended desktop displays, LTTPRs are essential to ensure reliable performance without compromising bandwidth.

How LTTPRs Work with Link Training

DisplayPort link training involves multi-phase adjustments to signal amplitude and equalization. In a system with LTTPRs, this training is segmented:

- Source trains with LTTPR1

- LTTPR1 trains with LTTPR2 (if present)

- Final LTTPR trains with the sink

Each repeater maintains full transparency in AUX channel forwarding and timing propagation, ensuring the source and sink can complete overall link initialization seamlessly.

Trilinear’s DisplayPort controller IP includes embedded LTTPR awareness and supports deterministic training sequences even in repeater-rich systems. This enables plug-and-play operation across demanding signal chains from consumer devices to automotive-grade interconnects.

Interoperability with MST, DSC, and HDCP

LTTPR + MST (Multi-Stream Transport)

LTTPRs must relay MST-related AUX traffic transparently. Trilinear’s MST-enabled DisplayPort IP works with repeaters to manage stream mapping, sideband communication, and bandwidth negotiation across multiple displays, even if routed through repeater chains. This is vital for daisy-chained docking stations or digital cockpits with shared links.

LTTPR + DSC (Display Stream Compression)

Display Stream Compression allows for bandwidth-efficient transmission of high-resolution video. While DSC itself is negotiated before link training, the presence of LTTPRs means that training and clock recovery timing must remain stable for compressed streams. Trilinear’s IP ensures signal integrity and decoder compatibility across compressed, repeater-extended DisplayPort links.

LTTPR + HDCP 2.3

HDCP encryption relies on tightly timed AUX transactions. If the repeater mishandles or delays authentication messages, the session can fail. Trilinear’s controller includes AUX buffering and repeater-safe HDCP pathways to preserve secure content delivery even across multi-hop LTTPR topologies.

Automotive Applications with DP AE and LTTPR

Automotive platforms increasingly demand multi-display environments: instrument clusters, center consoles, passenger screens, and even mirror replacements. These displays often sit far from the central processing unit, requiring long, shielded cable runs and stringent EMI controls.

LTTPRs enable DisplayPort to extend across these links while remaining compliant with DisplayPort Automotive Extensions (DP AE) and ISO 26262 functional safety principles. Trilinear’s IP is designed for ASIL B-ready systems and supports repeater-based topologies in safety-critical display architectures.

Design Considerations and Compliance

Incorporating LTTPRs affects several layers of system design:

- AUX forwarding logic must handle repeater addressing and transparent message relay.

- Link training timing must be managed carefully across segmented domains.

- Compliance testing now includes repeater-based link scenarios, with VESA CTS support for LTTPR paths.

Trilinear’s DisplayPort IP is engineered to reduce risk in these areas. Our IP offers:

- Built-in LTTPR segment handling

- Timing compensation features

- HDCP and MST interoperability

- Pre-validation for UHBR repeater scenarios

Conclusion

LTTPR is no longer an optional feature, it’s a design necessity for scalable, high-performance DisplayPort systems. Whether supporting 8K monitors through a docking station or delivering high-res automotive displays across shielded cable runs, LTTPRs provide the signal integrity and protocol transparency required for next-generation designs.

Trilinear Technologies offers DisplayPort IP built with LTTPR, MST, HDCP, and automotive support in mind, enabling reliable video delivery across the most demanding interconnect environments. Our controller IP is not only DisplayPort 2.1-ready but engineered for the long haul in more ways than one.

Related Semiconductor IP

- DisplayPort Receiver IP

- DisplayPort Transmitter IP

- HDCP 2 on HDMI / DisplayPort Embedded Security Module Firmware (generation 3)

- 4-port Receiver/Transmitter/Repeater HDCP 2.3 on HDMI 2.0 and/or DisplayPort 2.0/1.4 ESM (generation 3)

- 2-port Receiver/Transmitter/Repeater HDCP 2.3 on HDMI 2.0 and/or DisplayPort 2.0/1.4 ESM (generation 3)

Related Articles

- Understanding the "e" verification language

- Understanding the Semiconductor Intellectual Property (SIP) Business Process

- Understanding the MAC impact of 802.11e: Part 2 (By Simon Chung and Kamila Piechota, Silicon and Software Systems)

- Understanding the MAC impact of 802.11e: Part 1 (By Simon Chung and Kamila Piechota, Silicon and Software Systems)

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks