xilinx/ IP

Filter

Compare

763

IP

from

101

vendors

(1

-

10)

-

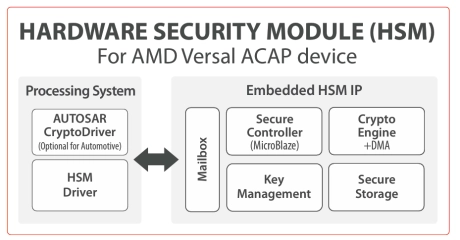

Hardware Security Module (HSM) for AMD Xilinx Versal ACAP device

- The HSM IP module is a Hardware Security Module for a wide range of applications.

- It is developed according to the guidelines set out by the EVITA project and is meant to be implemented on a AMD Xilinx Versal ACAP device.

- It supports TrustZone.

-

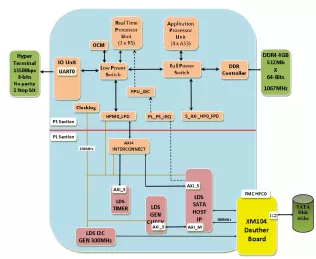

Xilinx Ultra Scale Plus SATA HOST IP

- Compliant with Serial ATA III specification and signaling rate is 6Gbs

- Xilinx Ultra Scale Plus GTHE4 FPGA

-

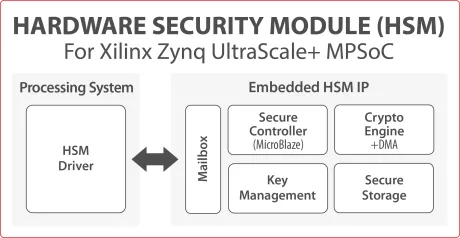

Hardware Security Module (HSM) for Xilinx Zynq UltraScale+ MPSoC platform

- The HSM IP module is a Hardware Security Module for a wide range of applications.

- It is developed, validated and licensed by Secure-IC (partner of Xilinx) as an FPGA-based IP solution dedicated to the Xilinx Zynq UltraScale+ MPSoC platform.

-

Gamma LUT

- Programmable gamma table supports gamma correction or any user defined function

- Three channel independent look-up table structure

- One, two, four or eight pixel-wide AXI4-Stream video interface

- 8 and 10 bits per component support

-

Sensor Demosaic

- RGB Bayer image sensor support

- One, two, four or eight pixel-wide AXI4-Stream video interface

- Supports 8, 10, 12, and 16 bits per color component

- Supports spatial resolutions from 64 x 64 up to 4,096 x 2160

-

Simulation Clock Generator

- Configurable frequency

- Single Ended/ Differential clock

- Configurable polarity of reset

- Configurable initial reset cycles

-

ETRNIC

- Support for End-point RDMA functionality

- 100Gb data path

- Support for hardware based reliable connection

- Hardware handshake on user interface

-

Interlaken Core (Up to 600G)

- Support for up to 600 Gbps of throughput

- Data striping and de-striping across 1 to 24 lanes

- Programmable BurstMax, BurstMin, BurstShort and MetaFrameSize parameters

- Support for Synchronization, Scrambler State, Diagnostic, and Skip Word Block Types

-

USXGMII Subsystem

- Designed to meet the USXGMII specification EDCS-1467841 revision 1.4

- Supports 10M, 100M, 1G, 2.5G, 5G, or 10GE data rates over a 10.3125 Gb/s link

- Both media access control (MAC) and physical coding sublayer/physical medium attachment (PCS/PMA) functions are included

- Code replication/removal of lower rates onto the 10GE link