xSPI IP

Filter

Compare

28

IP

from

12

vendors

(1

-

10)

-

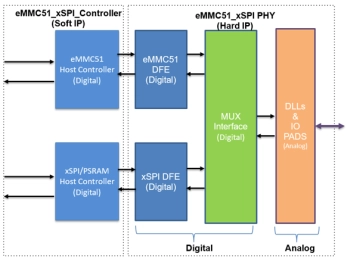

xSPI + eMMC Combo PHY IP

- This IP integrates both xSPI (Expanded Serial Peripheral Interface) and eMMC 5.1 PHY (Physical Layer) into a single unified solution, enabling support for two distinct memory protocols within the same IP.

- By combining the PHY layers for both interfaces, the design simplifies system integration, reduces area and pin count, and enhances design flexibility for SoCs that require both boot and high-speed storage functionality.

-

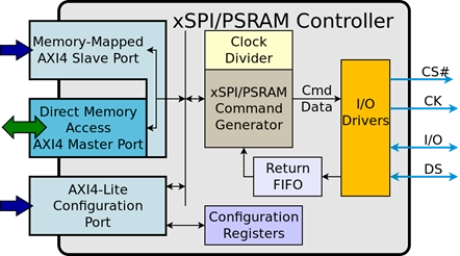

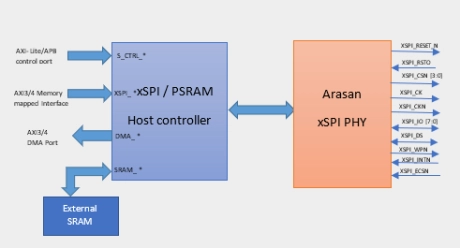

xSPI - PSRAM Master

- The xSPI/PSRAM master IP is easy to use, simple to work with, quick to operate, and reliable under all conditions. It supports the xSPI JESD~251 standard from a standard AXI3 or AXI4 slave interface.

- It also supports APMemory Octal/QSPI RAM, HyperRAM, HyperFlash, and features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces.

-

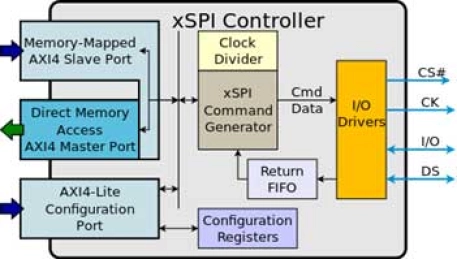

xSPI Master IP | NOR IP

This Universal NOR Flash IP supports a variety of NOR Devices and multiple Protocols, combines ease of use with high reliability, low power and speed under all conditions, including automotive applications.

The xSPI master IP supports the xSPI JESD251 standard from a standard AXI4 slave interface, and also features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces. Also supports JEDEC SFDP Standard.

-

xSPI PHY

- The xSPI PHY is designed to work with both the xSPI/PSRAM and the xSPI master host controller IPs. When coupled with the ACS xSPI PHY, the combined IPs are able to interact with SPI, Dual SPI, Quad SPI, Octal SPI, and xSPI devices at the full 200 MHz data rate.

- This includes both HyperRAM and HyperFlash protocols. Both single and dual data rate modes are supported. The xSPI Master controller IP supports flash devices, whereas the xSPI/PSRAM controller has been designed to support SRAM types of devices using the same interface.

-

xSPI Multiple Bus Memory Controller

- SLL’s unified xSPI Multiple Bus Memory Controller IP supports the widest range of JEDEC xSPI and xSPI-like NOR Flash and PSRAM memories (JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0, 2.0 and 3.0, OctaBus and Xccela Bus) that are available now from many memory vendors.

- JEDEC xSPI and xSPI-like memories offer good performance with lower hardware and power costs. Memory device variants offer up to 512 Mbit PSRAM, up to 2 Gigabit NOR Flash, up to 250 MHz DDR clock speeds, with x4, x8 and x16 data path widths, and a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints. Some PRSAM devices are now also available with internal ECC.

-

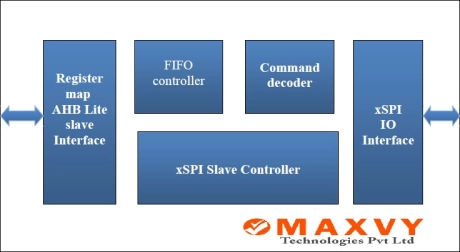

Expanded Serial Peripheral Interface (xSPI) Slave Controller

- The JESD251 Expanded Serial Peripheral Interface Slave controller is provides high data throughput, low signal count, and limited backward compatibility with legacy Serial Peripheral Interface(SPI) devices

- It is used to connect xSPI Master devices in computing, automotive, Internet of Things, Embedded system and mobile system processor to non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

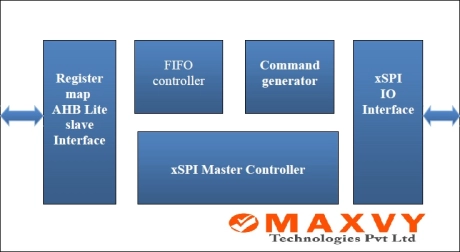

Expanded Serial Peripheral Interface (xSPI)Master Controller

- The Expanded Serial Peripheral Interface (JESD251) Master controller is low signal count, high data bandwidth, primarily for use in computing, automotive, Internet of Things, Embedded system and mobile system processor to connect multiple source of Serial Peripheral Interface (xSPI) slave devices like non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

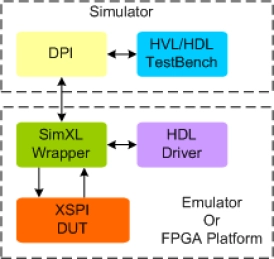

Simulation VIP for xSPI

- xSPI Profile 1

- SPI (Read Zero Latency), DUAL (1-1-2, 1-2-2), Quad (As per JESD251-A1), and Octal modes Data Rate: STR and DTR

- Modes

- SPI-STR (1S-1S-1S), QUAD-STR (4S-4S-4S), OCTAL-STR(8S-8S-8S), and OCTAL-DTR (8D-8D-8D) modes

-

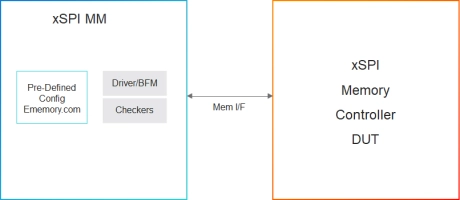

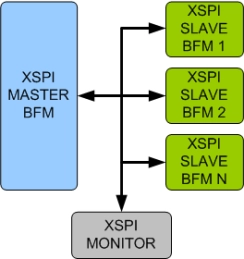

xSPI (Expanded Serial Peripheral Interface) Verification IP

- Follows xSPI basic specification as defined in JEDEC eXpanded Serial Peripheral Interface (xSPI)for Non Volatile Memory Devices.

- Fully compatible with JESD251 and JESD251-1 standards.

- Support Master and Slave Mode.

- Supports 4-wire, 7-wire, 8-wire, 11-wire and 12-wire interfaces.

-

XSPI (Expanded Serial Peripheral Interface) Synthesizable Transactor

- Follows XSPI basic specification as defined in JEDEC eXpanded Serial Peripheral Interface (xSPI)for Non Volatile Memory Devices

- Supports Master and Slave Mode

- Supports 4-wire,7-wire,11-wire interface

- Supports data width upto 8 bits