Ultra-Low-Power Temperature/Voltage Monitor in TSMC 40nm IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

Ultra-Low-Power Temperature/Voltage Monitor on TSMC 16nm FFC

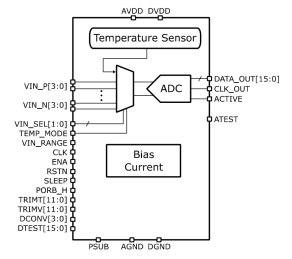

- The ODT-TVM-ULP-001C-16FFCT is an ultralow power temperature and voltage monitor designed in a 16nm standard TSMC process.

- This IP operates over the entire temperature range of - 40°C to 150°C.

- The temperature monitor achieves ±4C temperature accuracy without trim and ±1C temperature accuracy after a single room temperature trim.