USB4 IP

Filter

Compare

34

IP

from

9

vendors

(1

-

10)

-

USB4 PHY - TSMC N4P 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

-

USB4 PHY - TSMC N3E 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

-

USB4 PHY - TSMC N3P 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

-

USB4 VIP

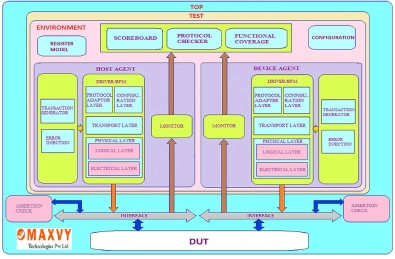

- The USB4 Verification IP (MX_USB4_VIP) provides a highly capable verification solution for the USB4 protocol which incorporating bus functional model (BFM), integrated protocol checkers and functional coverage along with assertion check

- The USB4 VIP can be readily customized and optimized for a wide range of specific system application

-

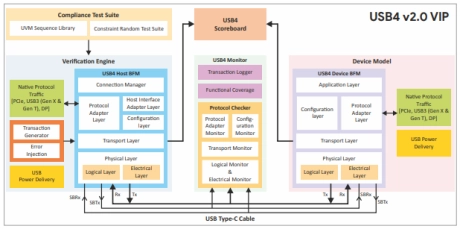

USB4 v2.0 Verification IP

- Fully compliant with USB4 specification v2.0 (October 2022) and Connection Manager version 2.0.

- Supports USB3.2 Specification, Revision 1.1 and backward compatibility to USB2.0.

- Supports USB Power Delivery Release 3.1, Version 1.8 and Type-C v2.2.

- Supports Thunderbolt (TBT3) interoperability.

-

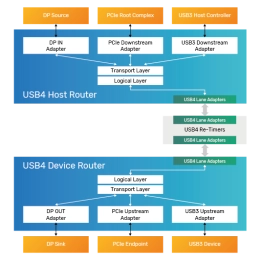

Simulation VIP for USB4

- Logical Layer

- Sideband channel

- Logical Layer State Machine

- GEN2, GEN3, and GEN4 speeds

-

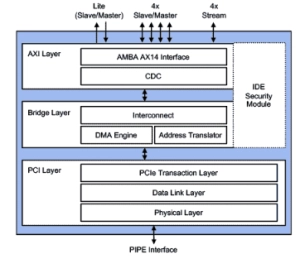

PCIe Controller for USB4 with AXI

- Internal data path size automatically scales up or down (64-, 256-, 512- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code – Gen5 support pending

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces

-

PCIe Controller for USB4

- Internal data path size automatically scales up or down (256-, 512- bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs (when supported)

- Ultra-low Transmit and Receive latency (excl. PHY)

-

USB4 PHY - TSMC N7 1.8V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

-

USB4 PHY - TSMC N6 1.8V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power