USB 2.0 OTG PHY SMIC IP

Filter

Compare

20

IP

from

4

vendors

(1

-

10)

-

USB 2.0 nanoPHY - SMIC 65LL, OTG

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB 2.0 picoPHY - SMIC 40LL25, OTG

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB 2.0 nanoPHY - SMIC 65LL25, 2-port OTG

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB 2.0 femtoPHY - SMIC 40LL25 x1, OTG

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB 2.0 femtoPHY - SMIC 28HKMG18 x1, OTG, North/South (vertical) poly orientation

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

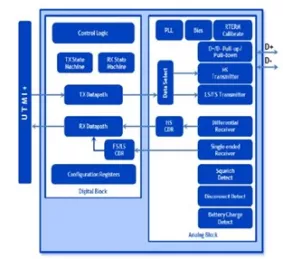

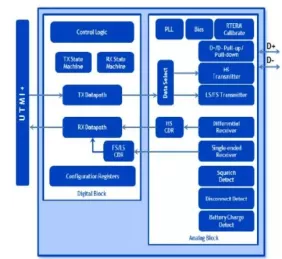

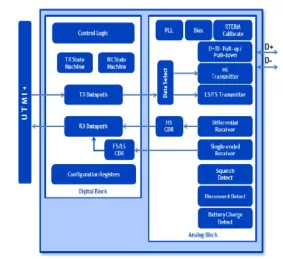

USB 2.0 PHY IP, Silicon Proven in SMIC 12SF++

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in SMIC 40LL

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in SMIC 55LL

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in SMIC 14SF+

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip