Trilinear Technologies IP

Filter

Compare

8

IP

from

1

vendors

(1

-

8)

-

HDCP Authentication Software Stack

- The High-bandwidth Digital Content Protection (HDCP) Authentication Software Stack implements HDCP capability in a Trilinear DisplayPort interface (transmitter or receiver IP core) or the Trilinear HDCP Encryption-Decryption Engine core.

-

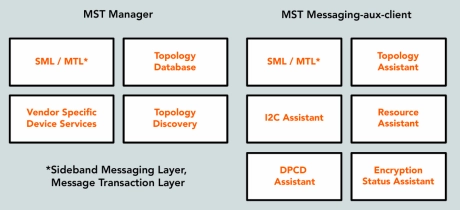

MST Topology Management Stack

- The DisplayPort Multi Stream Transport (MST) Topology Management Software implements MST topology management for multiple monitors on a Trilinear DisplayPort Transmitter IP core.

- The software enables customers to shorten time to market and reduce design risk using pre-tested, ready-to-deploy software.

-

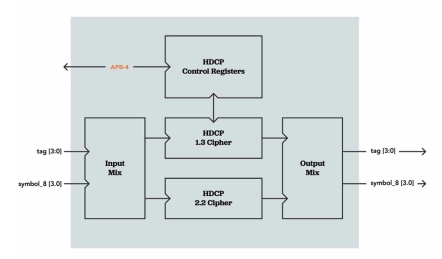

HDCP Encryption-Decryption Engine

- Real-time encryption/decryption

- 8k compression available for select applications

- Low gate count and low latency implementation

- Supports HDCP 1.3 and 1.4

-

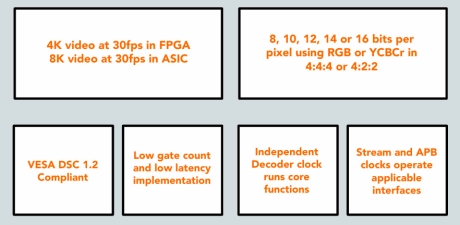

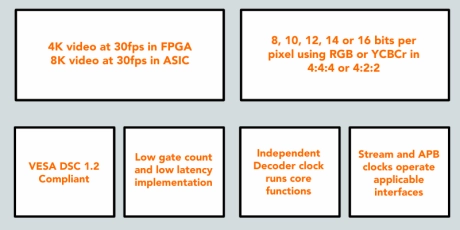

Display Stream Compression (DSC 1.2) Encoder

- The Display Stream Compression (DSC) Encoder offers real-time compression of high-definition streams with resolutions up to 8K.

- The core supports 8, 10, 12, 14 or 16 bits per pixel input using either RGB or YCbCr in 4:4:4 or 4:2:2 format.

- The DSC Encoder core integrates industry standard interfaces for host configuration and control, video input, and output.

-

Display Stream Compression (DSC 1.2) Decoder

- The Display Stream Compression (DSC) Decoder core offers realtime decompression of high-definition streams with resolutions from 480 to 8K.

- The core supports 8, 10, 12, 14 or 16 bits per pixel using either RGB or YCbCr in 4:4:4 or 4:2:2 format.

- The DSC Decoder core integrates industry standard interfaces for host configuration and control, data input, and video output.

-

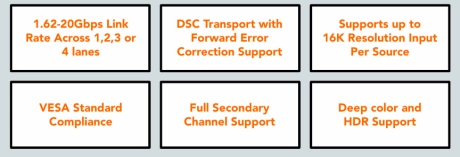

DisplayPort Transmitter IP

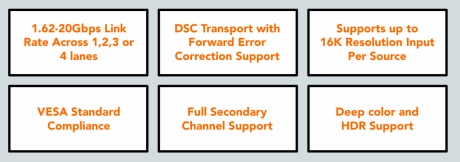

- Our 6th generation DisplayPort Transmitter Link Controller core supports DisplayPort 2.1, DisplayPort 1.4a and embedded DisplayPort 1.5.

- Features include link rates up to 20Gbps for DisplayPort 2.0, 8.1Gbps for DisplayPort 1.4a. Display Steam Compression (DSC), multi-stream transport (MST) and more. The base core includes all required link functionality— Main Link, Secondary Channel, and AUX Channel protocols—and supports the HDCP 2.3 standards for data encryption.

-

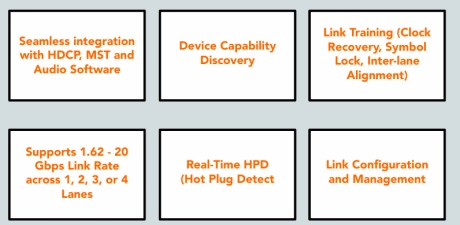

DisplayPort Link Policy Maker

- The DisplayPort Link Policy Maker (LPM) is a DisplayPort 1.4/2.0 compliant software stack that manages and controls the DisplayPort serial link and AUX channel communications.

- The software provides for enumeration and configuration of the source and sink devices, adaptive training of the DisplayPort link, video stream allocation and transmission, AUX channel traffic management and handling of all HPD (Hot Plug Detect) events.

-

DisplayPort Receiver IP

- Silicon proven on multiple ASIC and FPGA processes

- Capable of operating without a host CPU in low complexity applications

- Horizontal and vertical video delimiter signals with 1, 2 or 4 pixels per output cycle, supporting up to 16K resolution output; deep color and HDR support

- 1.62 to 8.1 Gbps link rate across 1, 2, or 4 lanes