TCPHardware Accelerator IP

Filter

Compare

455

IP

from

83

vendors

(1

-

10)

-

RSA Signature Verification Accelerator - Compact RSA Signature Verification Accelerator for Constrained Devices

- Compact RSA Signature Verification Accelerator for Constrained Devices

-

Crypto Box Toolset Secure Accelerator

- The High-Performance Hybrid Crypto Box IP core delivers maximum cryptographic throughput by combining classical asymmetric (RSA, ECC), symmetric (AES), and hashing (SHA-2/HMAC) engines with a dedicated post-quantum accelerator supporting ML-KEM (Kyber) and ML-DSA (Dilithium).

- Designed for performance-critical systems without tight area or power limitations, this IP enables ultra-fast key exchange, digital signatures, and secure data processing.

-

Crypto Box Toolset Secure Accelerator

- The Hybrid Crypto Box IP core is a comprehensive, high-efficiency cryptographic solution that combines RSA, ECC, AES, and SHA-2/HMAC with a built-in accelerator for post-quantum algorithms such as ML-KEM (Kyber) and ML-DSA (Dilithium). Designed for embedded systems with balanced resource constraints, it enables secure key exchange, digital signatures, authenticated encryption, and hashing, future-proofed for the quantum era.

-

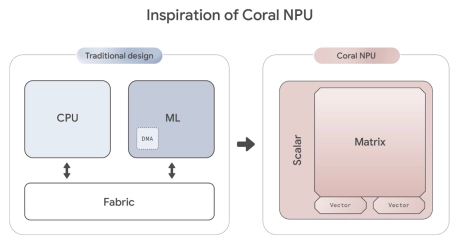

RISC-V-Based, Open Source AI Accelerator for the Edge

- Coral NPU is a machine learning (ML) accelerator core designed for energy-efficient AI at the edge.

- Based on the open hardware RISC-V ISA, it is available as validated open source IP, for commercial silicon integration.

-

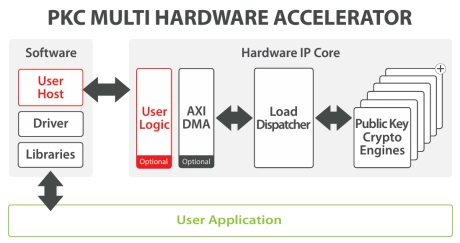

PKC Multi Hardware Accelerator IP

- The PKC Multi hardware accelerator is a secure connection engine that can be used to offload the compute intensive Public Key operations (Diffie-Hellman Key Exchange, Signature Generation and Verification), widely used for High-performance TLS Handshake.

-

Asymmetric cryptographic accelerator

- The ACrypto Engine is an asymmetric cryptographic accelerator suitable for embedded application.

- It provides capability for basic arithmetic and frequently used operations. Along with driver, it is flexible to support popular upperlayer applications.

-

Graphic 2D Accelerator

- The Graphic 2D Accelerator (G2D) is a specialized DMA dedicated to image manipulation.

-

Neural Network Accelerator

- The Neural-Network Accelerators (NACC) improves the inference performance of neural networks.

- The NACC data type is INT8, and supports im2col, convolution, depthwise convolution, average pool, max pool, fully connected, activation and matrix multiplication acceleration.

-

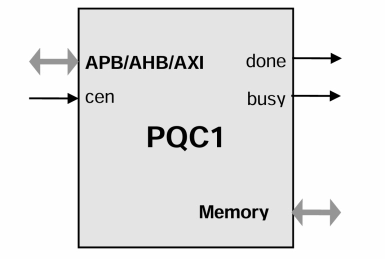

APB Post-Quantum Cryptography Accelerator IP Core

- Implements ML-KEM and ML-DSA post-quantum cryptography digital signature standards. The system interface is an microprocessor slave bus (APB, AHB, AXI options are available).

- The design is fully synchronous and requires only minimal CPU intervention due to internal microprogramming sequencer.