Sidense IP

Filter

Compare

1,188

IP

from

91

vendors

(1

-

10)

-

This IP is specially designed for anti-tamper protection which includes both current sense & voltage sense.

- Process: GSMC 0.18um 1P6M logic process

- Supply voltage: 2V~3.6V

- Voltage detectors & Current detectors

- Operating junction temperature: -40°C≤TJ≤+125°C

-

Crystal Oscillator for a 32 kHz Crystal - GLOBALFOUNDRIES® 22FDX®

- Specific crystal: 32 kHz

- Supported series resistance: up to 100 kOhm

- Supported load capacitance: 3 pF to 12.5 pF

- Startup time: 59 ms (TT, 12 pF) depending on crystal and PCB

-

Stand-Alone ESD Cell in GF 28nm

- This ESD library is a silicon-proven set of discrete, pad-independent ESD clamps for GlobalFoundries 28nm technology.

- The library is designed to provide robust ESD protection for power domains and low-speed signals in advanced SoCs where traditional pad-based protection is insufficient or impractical.

-

Ultra-low-power, low-cost sub-GHz 200 MHz – 950 MHz transceiver with PA for WSN

- The IoT and WSN transceiver IP targets long-range, low-power connectivity for dense sensor deployments and industrial networks

- Supporting sub-GHz 802.15.4g, Wi-SUN, and integrated 2.4 GHz operation, these designs provide excellent receiver sensitivity, flexible modulation support, and ultra-low energy consumption

- They are ideal for smart meters, building automation, grid monitoring, and wide-area IoT systems.

-

Ultra-low-power, low-cost sub-GHz transceiver for WSN

- The IoT and WSN transceiver IP targets long-range, low-power connectivity for dense sensor deployments and industrial networks

- Supporting sub-GHz 802.15.4g, Wi-SUN, and integrated 2.4 GHz operation, these designs provide excellent receiver sensitivity, flexible modulation support, and ultra-low energy consumption

- They are ideal for smart meters, building automation, grid monitoring, and wide-area IoT systems.

-

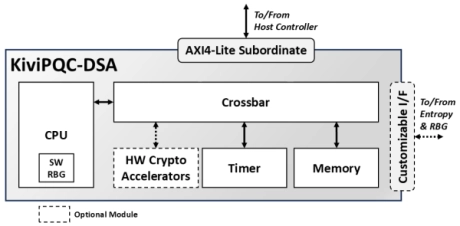

ML-DSA Digital Signature Engine

- The KiviPQC™-DSA is a hardware accelerator for post-quantum cryptographic operations.

- It implements the Module Lattice-based Digital Signature Algorithm (ML-DSA), standardized by NIST in FIPS 204.

- This mechanism realizes the appropriate procedures for securely generating a private/public key pair, digitally signing a message or a data block, and performing digital signature verification.

-

Tiny, Ultra-Low-Power Embedded RISC-V Processor

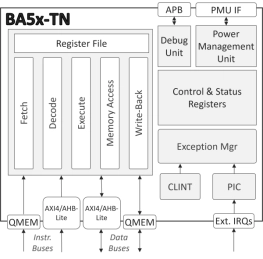

- The BA5x-TN is a compact, ultra-low power, 32-bit, deeply embedded processor IP core.

- With a two-stage execution pipeline, the processor implements the Embedded variant of the base RV32 ISA (RV32E).

- It uses just 16 general-purpose compressed instructions and omits other resource-demanding extensions.

-

Low-Power Embedded RISC-V Processor

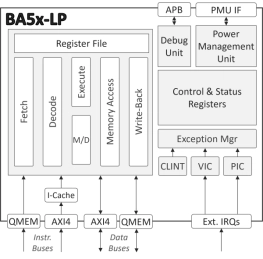

- The BA5x-LP is a highly efficient, low-power, 32-bit, deeply embedded processor IP core.

- The two-stage pipeline processor implements either the RV32I or RV32E instruction set.

- It comes pre-configured with the Multiply/Divide (M) and Compressed Instruction (C) extensions, providing a more flexible and capable platform without a significant increase in area or power.

-

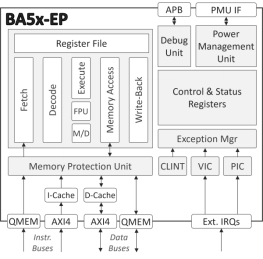

Enhanced-Processing Embedded RISC-V Processor

- The BA5x-EP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for complex, processing-demanding applications.

- It is equipped with a floating-point unit and cache memories, supports hardware-level virtualization, and is suitable for concurrent execution in a multi-processor environment.