SATA 6G IP

Filter

Compare

106

IP

from

8

vendors

(1

-

10)

-

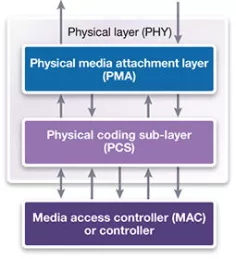

SATA 6G PHY in GF (40nm, 28nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY

- ? 6-Gbps transmission rate through standard SATA cable

- ? Spread-spectrum clock (SSC) generation and absorption

- ? Programmable down-spread (+4,980 ppm through -4,980 ppm)

- ? Fully clock-forwarded transceiver interface, configurable using soft PMA layer above hard macro PHY

-

SATA 6G Host Controller IP

- Compliant with SATA/eSATA v3.3 and SATA PIPE v4.3 specifications

- Memory data protection and memory address parity protection

- Hardware support for native nommand queuing (NCQ)

- End-to-end parity data path protection

-

SATA 6G Device Controller IP

- Compliant with SATA/eSATA v3.3 and SATA PIPE v4.3 specifications

- Memory data protection and memory address parity protection

- Hardware support for native nommand queuing (NCQ)

- End-to-end parity data path protection

-

SATA 6G PHY in UMC (40nm, 28nm, 22nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY in TSMC (40nm, 28nm, 16nm, 12nm, N7)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY in SMIC (40nm, 28nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

PCIe 2.0/ CEI 6G, GF 22FDSOI x4, North/South (vertical) poly orientation

- Supports 1.25 to 6.25 Gbps data rates

- Supports PCI Express 2.1/1.1, SATA 6G/3G/1.5G, XAUI, SGMII, CEI-6G specifications

- Supports x1 to x16 macro configurations

- Superior signal integrity enabled by adaptive continuous time linear equalizer (CTLE), and feed forward equalization (FFE)

-

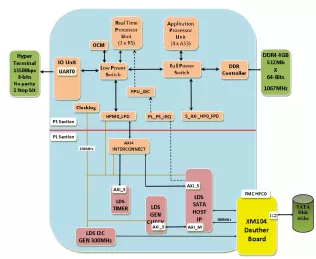

Xilinx Ultra Scale Plus SATA HOST IP

- Compliant with Serial ATA III specification and signaling rate is 6Gbs

- Xilinx Ultra Scale Plus GTHE4 FPGA